# **Preliminary User's Manual**

# μPD780828A Subseries

8-bit Single-Chip Microcontroller

μPD780824A μPD780826A μPD780828A μPD78F0828A

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

- The information in this document is current as of 28.01, 2003. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other

intellectual property rights of third parties by or arising from the use of NEC Electronics products

listed in this document or any other liability arising from the use of such NEC Electronics products.

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual

property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC Electronics no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics

products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated

entirely. To minimize risks of damage to property or injury (including death) to persons arising from

defects in NEC Electronics products, customers must incorporate sufficient safety measures in their

design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools,

personal electronic equipment and industrial robots.

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems,

anti-disaster systems, anti-crime systems, safety equipment and medical equipment

(not specifically designed for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems,

life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics 's willingness to support a given application.

**Notes:** 1. " NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

2. " NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.10

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Europe) GmbH

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

#### Sucursal en España

Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

## Filiale Italiana

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

## **Branch The Netherlands**

Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### **Branch Sweden**

Taeby, Sweden

Tel: 08-63 80 820

Fax: 08-63 80 388

# **United Kingdom Branch**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### NEC Electronics Singapore Pte. Ltd.

Singapore

Tel: 65-6253-8311 Fax: 65-6250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos, Brasil

Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

#### **Preface**

#### Readers

This manual has been prepared for engineers who want to understand the functions of the  $\mu$ PD780828A Subseries and design and develop its application systems and programs.

# μPD780828A Subseries:

$\begin{array}{l} \mu PD780824A(A),\ \mu PD780826A(A),\ \mu PD780828A(A),\ \mu PD780824A(A1),\ \mu PD780826A(A1),\ \mu PD780824A(A2),\ \mu PD780824A(A2),\ \mu PD780828A(A2) \end{array}$

#### **Purpose**

This manual is intended for users to understand the functions of the  $\mu PD780828A$  Subseries.

#### Organization

The  $\mu$ PD780828A subseries manual is separated into two parts: this manual and the instruction edition (common to the 78K/0 series).

μPD780828A Subseries This Manual 78K/0 series User's Manual Instruction

- Pin functions

- · Internal block functions

- Interrupt

- Other on-chip peripheral functions

- CPU functions

- · Instruction set

- Explanation of each instruction

#### **How to Read This Manual**

Before reading this manual, you should have general knowledge of electric and logic circuits and microcontrollers.

- When you want to use this manual as the manual for (A) products, (A1) products, and (A2) products:

- $\rightarrow$  Only the quality grade differs between (A), (A1) and (A2) products.

Read the part number as follows:

$$\begin{split} \mu PD780824A &\rightarrow \mu PD780824A(A), \ \mu PD780824A(A1), \ \mu PD780824A(A2) \\ \mu PD780826A &\rightarrow \mu PD780826A(A), \ \mu PD780826A(A1), \ \mu PD780826A(A2) \\ \mu PD780828A &\rightarrow \mu PD780828A(A), \ \mu PD780828A(A1), \ \mu PD780828A(A2) \\ \mu PD78F0828A &\rightarrow \mu PD78F0828A(A) \end{split}$$

- When you want to understand the function in general:

- $\rightarrow$  Read this manual in the order of the contents.

- How to interpret the register format:

- → For the bit number enclosed in square, the bit name is defined as a reserved word in RA78K/0, and in CC78K/0 and defined in the header file of hte IAR compiler.

- To make sure the details of the registers when you know the register name.

- $\rightarrow$  Refer to Appendix C.

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# • Related documents for µPD780828A Subseries

| Document name                          | Document No. |         |  |

|----------------------------------------|--------------|---------|--|

| Document name                          | Japanese     | English |  |

| μPD780828A Subseries User's Manual     | Planned      | U16387E |  |

| 78K/0 Series User's Manual-Instruction | IEU-849      | U12326E |  |

| 78K/0 Series Instruction Table         | U10903J      | -       |  |

| 78K/0 Series Instruction Set           | U10904J      | -       |  |

# • Related documents for development tools (User's Manuals)

| Document name                                       | Document No.                      |         |           |

|-----------------------------------------------------|-----------------------------------|---------|-----------|

| Document name                                       | Japanese                          | English |           |

| RA78K Series Assembler Package                      | Operation                         | EEU-809 | EEU-1399  |

| KATON Selles Assembler Fackage                      | Language                          | EEU-815 | EEU-1404  |

| RA78K Series Structured Assembler Preproces         | ssor                              | EEU-817 | EEU-1402  |

| CC78K Series C Compiler                             | Operation                         | EEU-656 | EEU-1280  |

| CC/or Series C Compiler                             | Language                          | EEU-655 | EEU-1284  |

| CC78K/0 C Compiler                                  | Operation                         | U11517J | -         |

| CC76NV0 C Compiler                                  | Language                          | U11518J | -         |

| CC78K/0 C Compiler Application Note Programming Not |                                   | EEA-618 | EEA-1208  |

| CC78K Series Library Source File                    |                                   | EEU-777 | -         |

| IE-78K0-NS-A                                        |                                   | U14889J | U14889E   |

| IE-78K0-NS-P04                                      |                                   | -       | U13357E   |

| IE-780828-NS-EM4                                    |                                   | Planned | - U13337E |

| NP-80GC-TQ                                          |                                   | -       | -         |

| SM78K0 System Simulator Windows™ Base               | Reference                         | U15373J | U15373E   |

| SM78K0 Series System Simulator                      | External part user open Interface | U15802J | U15802E   |

| ID78K0-NS Integrated Debugger Windows Base  Guide   |                                   | U15185J | U15185E   |

# **Preface**

# • Related documents for embedded software (User's Manual)

| Document name                                                                     |              | Document No. |          |

|-----------------------------------------------------------------------------------|--------------|--------------|----------|

| Document                                                                          | name         | Japanese     | English  |

|                                                                                   | Basics       | U11537J      | -        |

| 78K/0 Series Real-Time OS                                                         | Installation | U11536J      | -        |

|                                                                                   | Technical    | U11538J      | -        |

| 78K/0 Series OS MX78K0 Basics                                                     |              | EEU-5010     | -        |

| Fuzzy Knowledge Data Creation Tool                                                | EEU-829      | EEU1438      |          |

| 78K/0, 78K/II, 87AD Series Fuzzy Infe<br>tem-Translator                           | EEU-862      | EEU-1444     |          |

| 78K/0 Series Fuzzy Inference Develop Inference Module                             | EEU-858      | EEU-1441     |          |

| 78K/0 Series Fuzzy Inference Development Support System- Fuzzy Inference Debugger |              | EEU-921      | EEU-1458 |

# • Other Documents

| Document name                                                     | Document No. |          |

|-------------------------------------------------------------------|--------------|----------|

| Document name                                                     | Japanese     | English  |

| IC Package Manual                                                 | C10943X      | -        |

| Semiconductor Device Mounting Technology Manual                   | C10535J      | C10535E  |

| Quality Grade on NEC Semiconductor Devices                        | C11531J      | C11531E  |

| Reliability Quality Control on NEC Semiconductor Devices          | C10983J      | C10983E  |

| Electric Static Discharge (ESD) Test                              | MEM-539      | -        |

| Semiconductor Devices Quality Assurance Guide                     | MEI-603      | MEI-1202 |

| Microcontroller Related Product Guide - Third Party Manufacturers | U11416J      | -        |

Caution: The above documents are subject to change without prior notice. Be sure to use the latest version document when starting design.

#### **Preface**

**Legend** Symbols and notation are used as follows:

Weight in data notation: Left is high-order column, right is low order column

Active low notation :  $\overline{xxx}$  (pin or signal name is over-scored) or

/xxx (slash before signal name)

Memory map address: : High order at high stage and low order at low stage

Note : Explanation of (Note) in the text

Caution : Item deserving extra attention

**Remark** : Supplementary explanation to the text

$\mbox{Numeric notation} \qquad : \mbox{ Binary} \ldots \mbox{xxxx or xxxB}$

Decimal . . . xxxx

Hexadecimal . . . xxxxH or 0x xxxx

Prefixes representing powers of 2 (address space, memory capacity)

$K \text{ (kilo)} : 2^{10} = 1024$

M (mega) :  $2^{20} = 1024^2 = 1,048,576$ G (giga) :  $2^{30} = 1024^3 = 1,073,741,824$

# **Table of Contents**

|              | Prefa     | ce                                                                        | . 5  |

|--------------|-----------|---------------------------------------------------------------------------|------|

| <b>0</b> 1 4 | 4 0 4"    | / BD700000                                                                | ٥-   |

| Chapter      |           | ne (µPD780828A Subseries)                                                 |      |

| 1.1          |           | es                                                                        |      |

| 1.2          |           | ation                                                                     |      |

| 1.3          |           | ng Information                                                            |      |

| 1.4          |           | Grade                                                                     |      |

| 1.5          |           | nfiguration (Top View)                                                    |      |

| 1.6          |           | Series Expansion                                                          |      |

| 1.7          |           | Diagram                                                                   |      |

| 1.8          |           | ew of Functions                                                           |      |

| 1.9          | Differe   | nces between Flash and Mask ROM version                                   | . 33 |

| Chantar      | 2 Din E   | unction (µPD780828A Subseries)                                            | 25   |

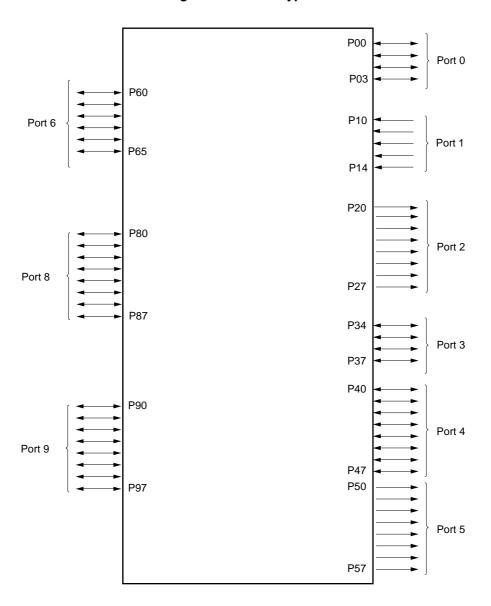

| Chapter 2.1  | Z FIII F  | nction List                                                               | 35   |

| 2.1          |           | ort Pins                                                                  |      |

| 2.2          |           | ption of Pin Functions                                                    |      |

| 2.3          | 2.3.1     | P00 to P03 (Port 0)                                                       |      |

|              | 2.3.1     | P10 to P14 (Port 1)                                                       |      |

|              | 2.3.2     | P20 to P27 (Port 2)                                                       |      |

|              | 2.3.3     | P34 to P37 (Port 3)                                                       |      |

|              | 2.3.4     |                                                                           |      |

|              | 2.3.5     | P40 to P47 (Port 4)                                                       |      |

|              | 2.3.6     | P50 to P57 (Port 5)                                                       |      |

|              | 2.3.7     | P60 to P65 (Port 6)                                                       |      |

|              | 2.3.6     | P80 to P87 (Port 8)                                                       |      |

|              | 2.3.9     | CTXD                                                                      |      |

|              | 2.3.10    | CRXD                                                                      |      |

|              | 2.3.11    | CCLK                                                                      |      |

|              | 2.3.12    | COM0 to COM3                                                              |      |

|              | 2.3.13    | V <sub>I CD</sub>                                                         |      |

|              | 2.3.14    |                                                                           |      |

|              | 2.3.16    | AV <sub>DD</sub> / AV <sub>REF</sub>                                      | . 43 |

|              | 2.3.10    | RESET                                                                     |      |

|              | 2.3.17    | X1 and X2                                                                 |      |

|              | 2.3.10    | SMV <sub>DD</sub>                                                         |      |

|              | 2.3.19    | SMV <sub>SS</sub>                                                         |      |

|              | 2.3.21    |                                                                           |      |

|              | 2.3.21    | V <sub>DD0</sub> , V <sub>DD1</sub>                                       |      |

|              | 2.3.22    | V <sub>SS0</sub> , V <sub>SS1</sub><br>V <sub>PP</sub> (µPD78F0828A only) | . 44 |

|              | 2.3.24    | IC (Mask ROM version only)                                                |      |

| 2.4          |           | Circuits and Recommended Connection of Unused Pins                        |      |

| 2.7          | 1 111 1/0 |                                                                           | . 40 |

| Chapter      | 3 CPU     | Architecture                                                              | 51   |

| 3.1          |           | y Space                                                                   |      |

| -            | 3.1.1     | Internal program memory space                                             |      |

|              | 3.1.2     | Internal data memory space                                                |      |

|              | 3.1.3     | Special function register (SFR) area                                      |      |

|              | 3.1.4     | Data memory addressing                                                    |      |

| 3.2          |           | sor Registers                                                             |      |

|              | 3.2.1     | Control registers                                                         |      |

|              | 3.2.2     | General registers                                                         |      |

|              | 3.2.3     | Special function register (SFR)                                           |      |

| 3.3          |           | tion Address Addressing                                                   |      |

|              | 3.3.1     | Relative addressing                                                       |      |

|              |           |                                                                           |      |

|             |       | 3.3.2                                  | Immediate addressing                                                                    | 71                                    |

|-------------|-------|----------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------|

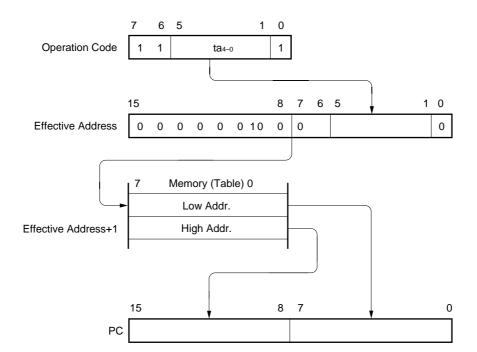

|             |       | 3.3.3                                  | Table indirect addressing                                                               |                                       |

|             |       |                                        |                                                                                         |                                       |

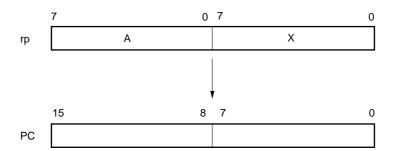

|             |       | 3.3.4                                  | Register addressing                                                                     |                                       |

|             | 3.4   | Operan                                 | d Address Addressing                                                                    | . 74                                  |

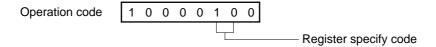

|             |       | 3.4.1                                  | Implied addressing                                                                      | 74                                    |

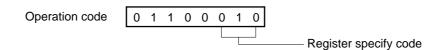

|             |       | 3.4.2                                  | Register addressing                                                                     | . 75                                  |

|             |       | 3.4.3                                  | Direct addressing                                                                       |                                       |

|             |       | 3.4.4                                  | Short direct addressing                                                                 |                                       |

|             |       | -                                      |                                                                                         |                                       |

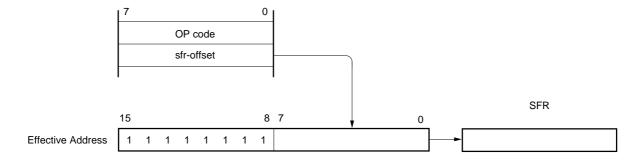

|             |       | 3.4.5                                  | Special function register (SFR) addressing                                              |                                       |

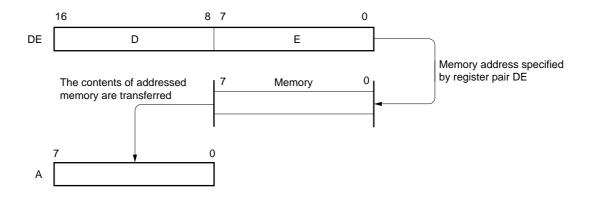

|             |       | 3.4.6                                  | Register indirect addressing                                                            | 79                                    |

|             |       | 3.4.7                                  | Based addressing                                                                        | 80                                    |

|             |       | 3.4.8                                  | Based indexed addressing                                                                | 81                                    |

|             |       | 3.4.9                                  | Stack addressing                                                                        |                                       |

|             |       | 00                                     |                                                                                         |                                       |

| Chan        | tor   | 1 Bort I                               | Eunations                                                                               | 02                                    |

| Chap        |       |                                        | Functions                                                                               |                                       |

|             | 4.1   |                                        | inctions                                                                                |                                       |

|             | 4.2   | Port Co                                | onfiguration                                                                            | 86                                    |

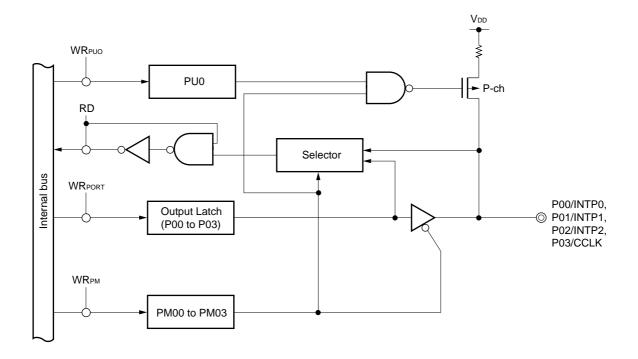

|             |       | 4.2.1                                  | Port 0                                                                                  | 87                                    |

|             |       | 4.2.2                                  | Port 1                                                                                  | 88                                    |

|             |       | 4.2.3                                  | Port 2                                                                                  |                                       |

|             |       | 4.2.4                                  |                                                                                         |                                       |

|             |       |                                        | Port 3                                                                                  |                                       |

|             |       | 4.2.5                                  | Port 4                                                                                  | -                                     |

|             |       | 4.2.6                                  | Port 5                                                                                  | 92                                    |

|             |       | 4.2.7                                  | Port 6                                                                                  | . 93                                  |

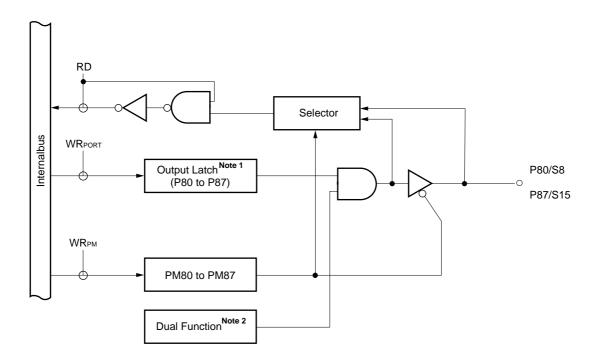

|             |       | 4.2.8                                  | Port 8                                                                                  | . 94                                  |

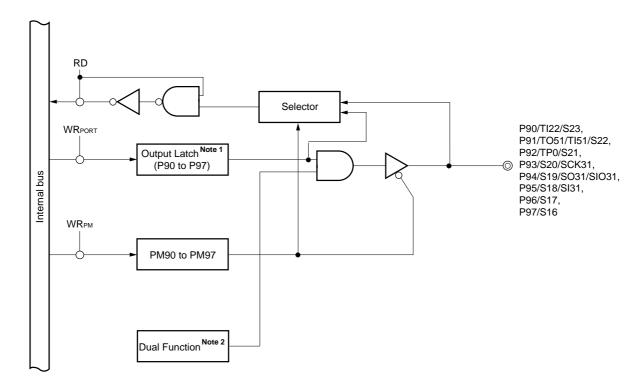

|             |       | 4.2.9                                  | Port 9                                                                                  |                                       |

|             | 4.3   |                                        | inction Control Registers                                                               |                                       |

|             | 4.4   |                                        | <del>-</del>                                                                            |                                       |

|             | 4.4   |                                        | Inction Operations                                                                      |                                       |

|             |       | 4.4.1                                  | Writing to input/output port                                                            |                                       |

|             |       | 4.4.2                                  | Reading from input/output port                                                          | . 100                                 |

|             |       | 4.4.3                                  | Operations on input/output port                                                         | . 101                                 |

|             |       |                                        |                                                                                         |                                       |

| Chap        | ter ! | 5 Clock                                | c Generator                                                                             | 103                                   |

| •           | 5.1   |                                        | Generator Functions                                                                     | 103                                   |

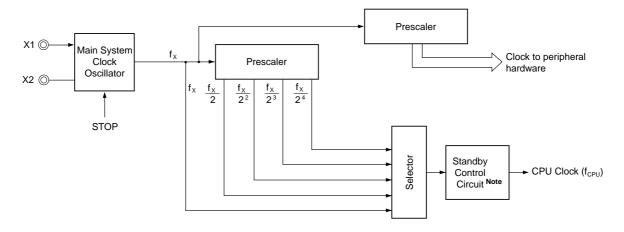

|             | 5.2   |                                        | Generator Configuration                                                                 |                                       |

|             | 5.3   |                                        | Generator Control Register                                                              |                                       |

|             |       |                                        |                                                                                         |                                       |

|             | 5.4   | •                                      | Clock Oscillator                                                                        |                                       |

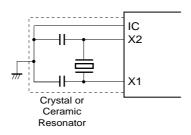

|             |       | 5.4.1                                  | Main system clock oscillator                                                            |                                       |

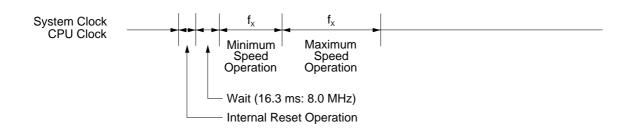

|             | 5.5   | Clock (                                | Generator Operations                                                                    | . 109                                 |

|             | 5.6   | Changi                                 | ng System Clock and CPU Clock Settings                                                  | 110                                   |

|             |       | 5.6.1                                  | Time required for switchover between system clock and CPU clock                         |                                       |

|             |       | 5.6.2                                  | System clock and CPU clock switching procedure                                          |                                       |

|             |       | 3.3.2                                  | 2, stem stock and or o stock officering procodule (111111111111111111111111111111111111 |                                       |

| Chan        | .4    | C 4C D:                                | 4 Times 0                                                                               | 442                                   |

| Chap        |       |                                        | t Timer 2                                                                               | _                                     |

|             | 6.1   |                                        | Timer 2 Functions                                                                       |                                       |

|             | 6.2   |                                        | Fimer 2 Configuration                                                                   |                                       |

|             | 6.3   | 16-Bit 7                               | Fimer 2 Control Registers                                                               | 116                                   |

|             | 6.4   | 16-Bit 7                               | Fimer 2 Operations                                                                      | 119                                   |

|             | _     | 6.4.1                                  | Pulse width measurement operations                                                      |                                       |

|             | 6.5   |                                        | Fimer 2 Precautions                                                                     |                                       |

|             | 0.5   | וט-טונ ו                               | innoi 4 i locaunona                                                                     | 123                                   |

| <b>O</b> I. |       | 7 0 514                                | Thus and Thus and Annual and EA                                                         | 405                                   |

| Chap        |       |                                        | Timer/Event Counters 50 and 51                                                          |                                       |

|             | - 4   | 8-Rit Ti                               | mer/Event Counters 50 and 51 Functions                                                  | 125                                   |

|             | 7.1   | 0 5.0                                  |                                                                                         |                                       |

|             | 7.1   | 7.1.1                                  | 8-bit operation modes                                                                   | 126                                   |

|             | 7.1   |                                        | 8-bit operation modes                                                                   |                                       |

|             |       | 7.1.1<br>7.1.2                         | 8-bit operation modes                                                                   | 128                                   |

|             | 7.2   | 7.1.1<br>7.1.2<br><b>8-Bit Ti</b>      | 8-bit operation modes                                                                   | . 128<br>. <b>129</b>                 |

|             |       | 7.1.1<br>7.1.2<br>8-Bit Ti<br>8-Bit Ti | 8-bit operation modes                                                                   | . 128<br>. <b>129</b><br>. <b>132</b> |

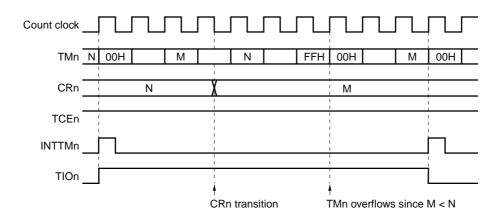

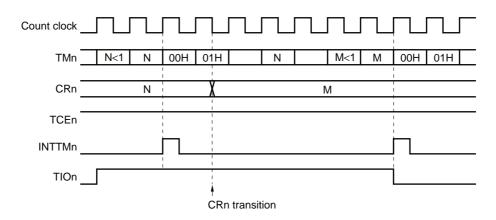

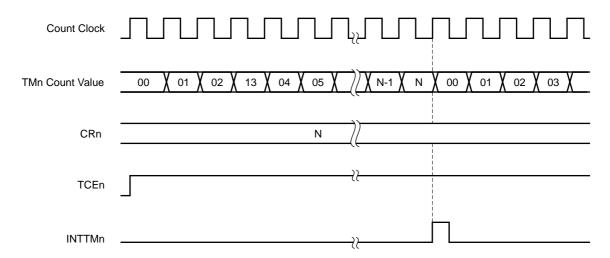

|              | 7.4.1              | Interval timer operations                  | 138 |

|--------------|--------------------|--------------------------------------------|-----|

|              | 7.4.2              | External event counter operation           | 143 |

|              | 7.4.3              | Square-wave output                         | 144 |

|              | 7.4.4              | PWM output operations                      | 146 |

| 7.           |                    | tion as interval timer (16-bit operation)  |     |

| 7.0          | 6 Cautio           | ns on 8-Bit Timer/Event Counters 50 and 51 | 153 |

|              |                    |                                            |     |

| Chapte       | r 8 8-Bit          | Timer 52                                   | 155 |

| 8.           | 1 8-Bit T          | imer 52 Functions                          | 155 |

| 8.2          | 2 8-Bit T          | imer 52 Configurations                     | 155 |

| 8.3          |                    | imer 52 Control Registers                  |     |

| 8.4          | 4 8-Bit T          | imer 52 Operations                         | 159 |

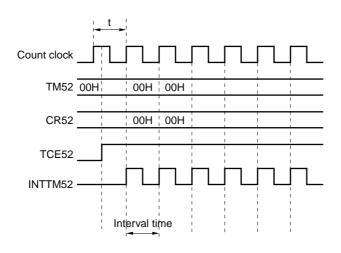

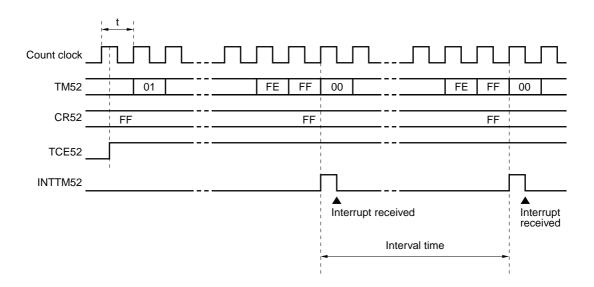

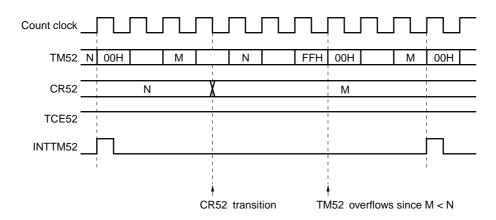

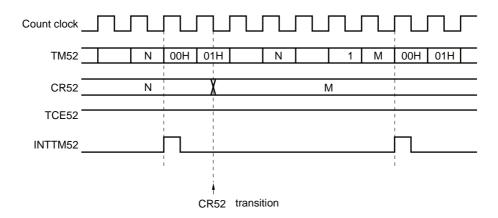

|              | 8.4.1              | Interval timer operations                  |     |

|              |                    | '                                          |     |

| Chapte       | r 9 Watc           | h Timer                                    | 163 |

| 9.           |                    | Timer Functions                            |     |

| 9.2          |                    | Timer Configuration                        |     |

| 9.:          |                    | Timer Mode Register (WTM)                  |     |

| 9.4          |                    | Timer Operations                           |     |

| ٠.           | 9.4.1              | Watch timer operation                      |     |

|              | 9.4.2              | Interval timer operation                   |     |

|              | 0                  |                                            |     |

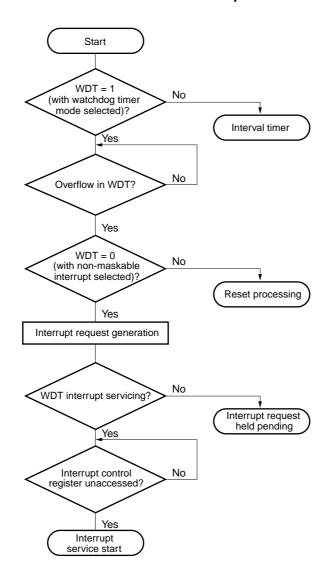

| Chante       | r 10 Watc          | hdog Timer                                 | 169 |

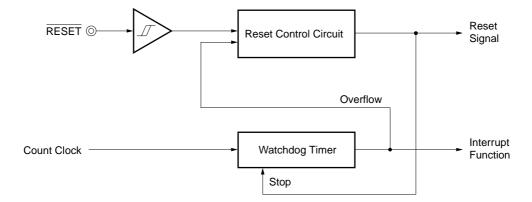

| 10           |                    | dog Timer Functions                        |     |

| 10           |                    | dog Timer Configuration                    |     |

| 10           |                    | dog Timer Configuration                    |     |

| _            |                    | dog Timer Operations                       |     |

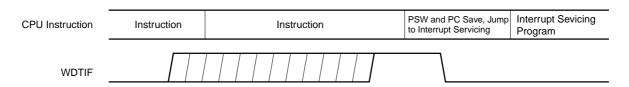

| 10           | 10.4.1             | Watchdog timer operation                   |     |

|              | 10.4.1             | Interval timer operation                   |     |

|              | 10.4.2             | interval timer operation                   | 173 |

| Chanto       | r 11 Clock         | k Output Control Circuit                   | 177 |

| -            |                    | Output Control Circuit Functions           |     |

|              |                    | Output Control Circuit Configuration       |     |

|              |                    | Output Function Control Registers          |     |

|              | .5 CIOCK           | Output I unction Control Neglisters        | 173 |

| Chanto       | r 12 A/D (         | Converter                                  | 191 |

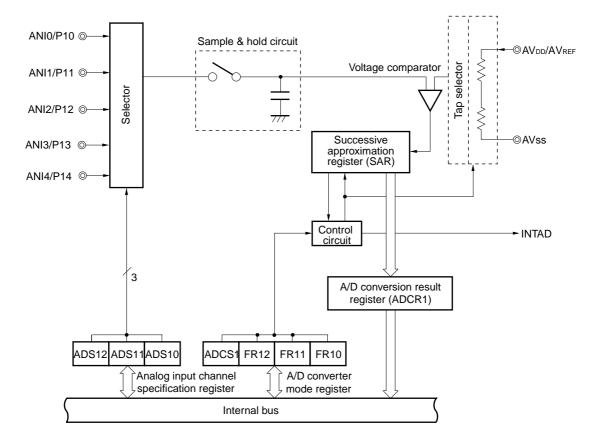

| •            |                    | onverter Functions                         |     |

|              |                    | onverter Configuration                     |     |

|              |                    | onverter Configuration                     |     |

|              |                    | onverter Operations                        |     |

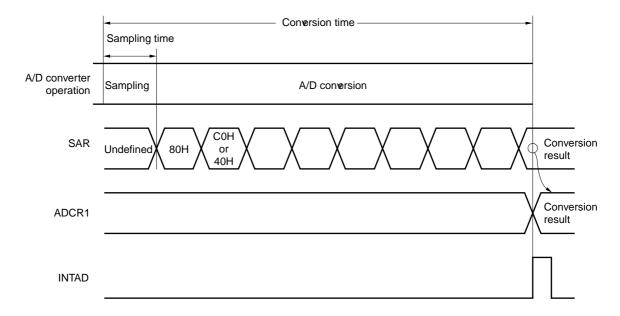

| 12           | 12.4.1             | Basic Operations of A/D Converter          |     |

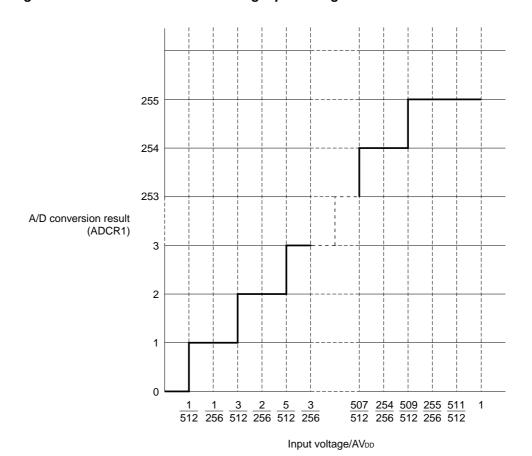

|              | 12.4.1             | Input voltage and conversion results       |     |

|              | 12.4.3             | A/D converter operation mode               |     |

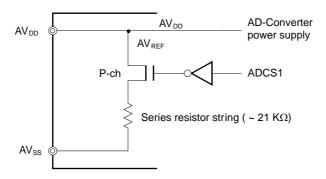

| 12           |                    | onverter Precautions                       |     |

|              |                    | ns on Emulation                            |     |

| 12           | o Caulio<br>12.6.1 | D/A converter mode register (DAM0)         |     |

|              | 12.0.1             | DIA converter mode register (DAMO)         | 130 |

| Chanto       | r 13 Soria         | ıl Interface SIO30                         | 107 |

| Chapte<br>13 |                    | Functions                                  |     |

| 13           |                    |                                            |     |

| _            |                    | Configuration                              |     |

| 13<br>13     |                    | SFRs (Special Function Registers)          |     |

| _            |                    | Interface Control Register                 |     |

| 13           |                    | Interface Operations                       |     |

|              | 13.5.1             | Operation stop mode                        |     |

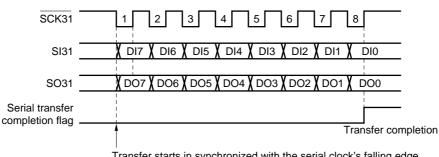

|              | 13.5.2             | Three-wire serial I/O mode                 | 201 |

| Charte       | , 11 C!-           | ıl Interface SIO31                         | 205 |

|              | r 14 Seria         |                                            | 205 |

|      | 14.2  |           | Configuration                                |     |

|------|-------|-----------|----------------------------------------------|-----|

|      | 14.3  | List of   | SFRs (Special Function Registers)            | 207 |

|      | 14.4  |           | nterface Control Register                    |     |

|      | 14.5  | Serial I  | nterface Operations                          | 210 |

|      |       | 14.5.1    | Operation stop mode                          | 210 |

|      |       | 14.5.2    | Three-wire serial I/O mode                   | 211 |

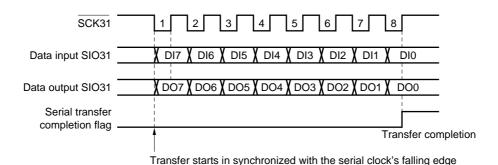

|      |       | 14.5.3    | Two-wire serial I/O mode                     |     |

|      |       |           |                                              |     |

| Char | ter 1 | 5 Seria   | I Interface Channel UART                     | 217 |

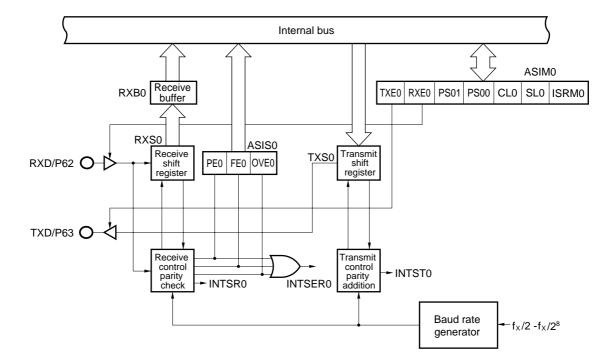

| ٦    | 15.1  |           | Functions                                    |     |

|      | 15.2  |           | Configuration                                |     |

|      | 15.3  |           | SFRS (Special Function Registers)            |     |

|      | 15.4  |           | nterface Control Registers                   |     |

|      | 15.5  |           | nterface Operations                          |     |

|      | 10.0  | 15.5.1    | Operation stop mode                          |     |

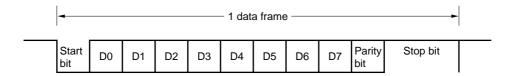

|      |       | 15.5.2    | Asynchronous serial interface (UART) mode    |     |

|      | 15.6  |           | or of UART during Standby of the Controller  |     |

|      | 13.0  | Dellavi   | of of OAIX1 during Standby of the Controller | 230 |

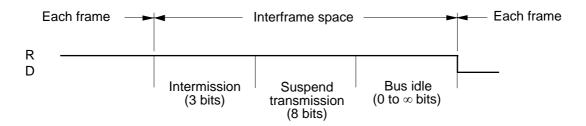

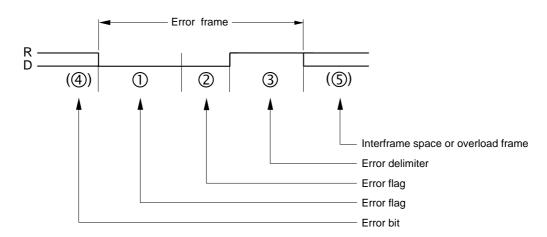

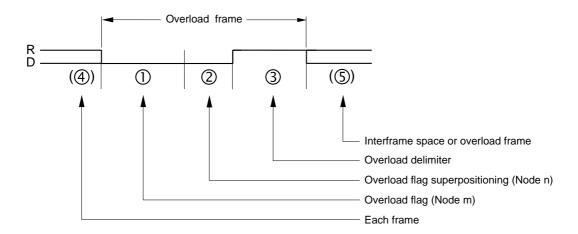

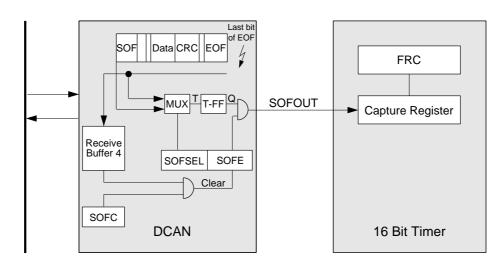

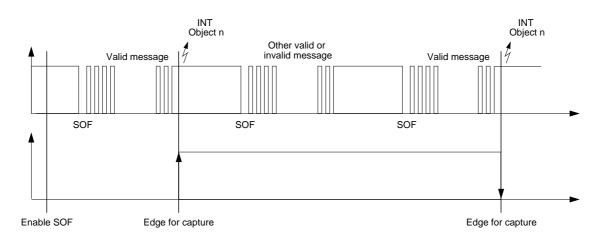

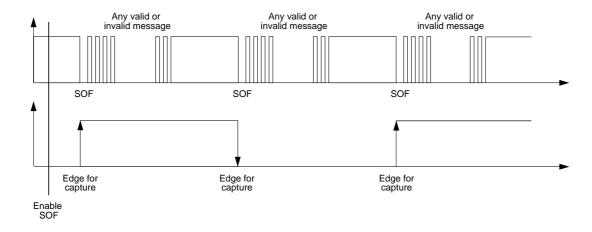

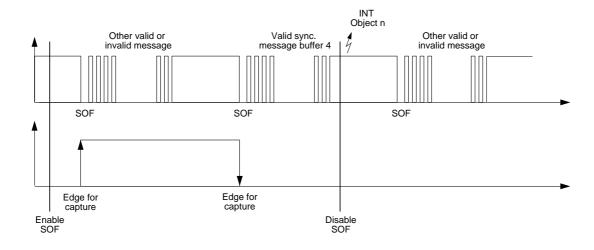

| Char | tor 1 | IS CAN    | Controller                                   | 20  |

| Cnap |       |           | rotocol                                      |     |

|      | 16.1  |           |                                              |     |

|      |       | 16.1.1    | Protocol Mode Function                       |     |

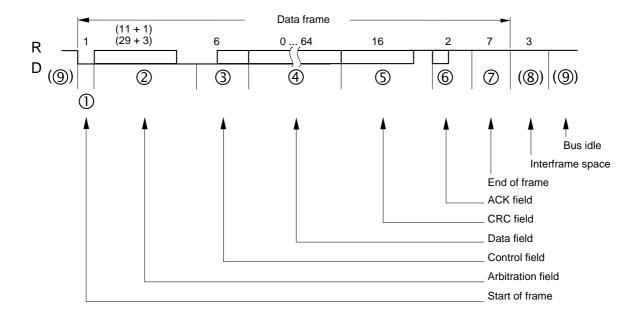

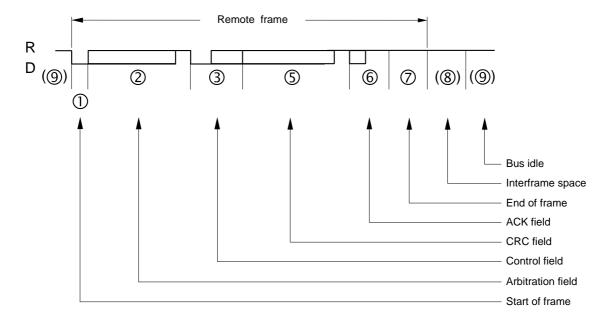

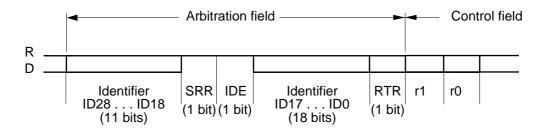

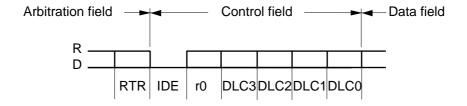

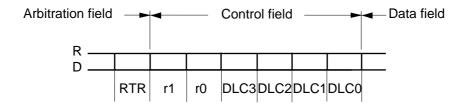

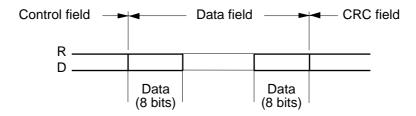

|      |       | 16.1.2    | Message Format                               |     |

|      |       | 16.1.3    | Data Frame / Remote Frame                    |     |

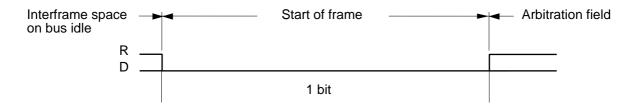

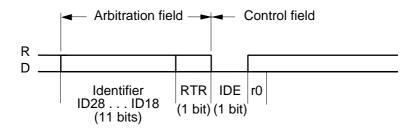

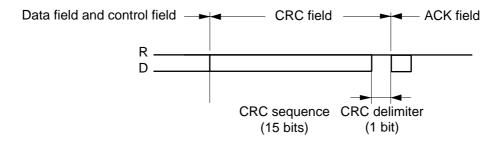

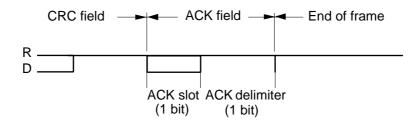

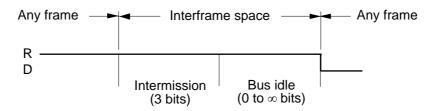

|      |       | 16.1.4    | Description of each field                    |     |

|      |       | 16.1.5    | Error Frame                                  |     |

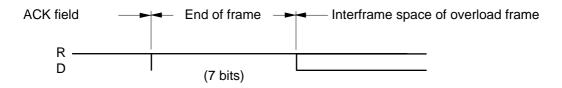

|      |       | 16.1.6    | Overload Frame                               |     |

|      | 16.2  |           | on                                           |     |

|      |       | 16.2.1    | Arbitration                                  |     |

|      |       | 16.2.2    | Bit Stuffing                                 |     |

|      |       | 16.2.3    | Multi Master                                 |     |

|      |       | 16.2.4    | Multi Cast                                   |     |

|      |       | 16.2.5    | Sleep Mode/Stop Function                     |     |

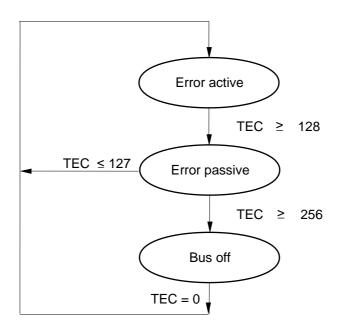

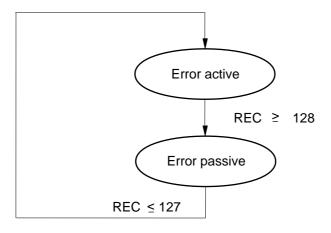

|      |       | 16.2.6    | Error Control Function                       |     |

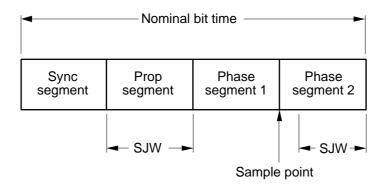

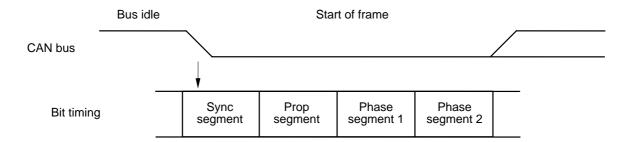

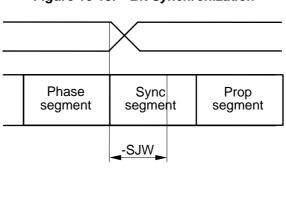

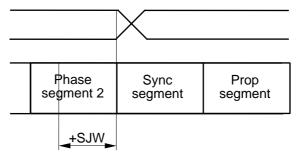

|      |       | 16.2.7    | Baud Rate Control Function                   |     |

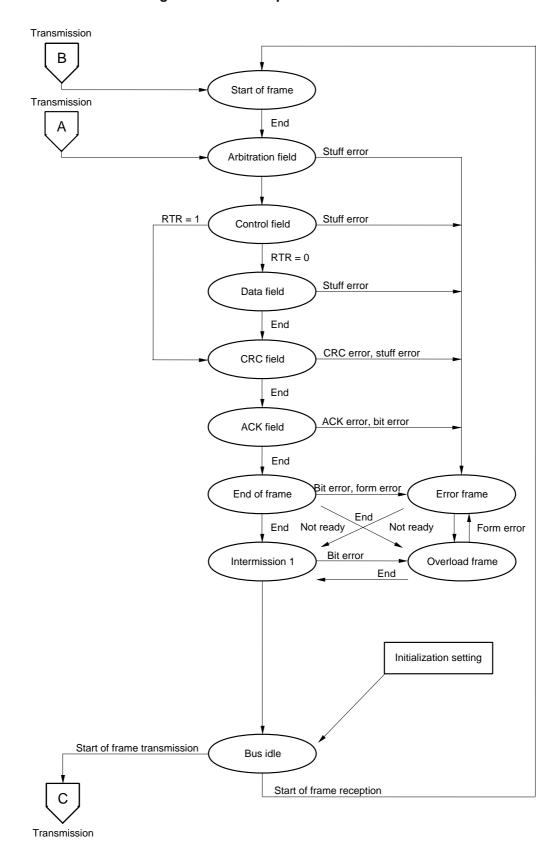

|      |       | 16.2.8    | State Shift Chart                            |     |

|      |       |           | Description                                  |     |

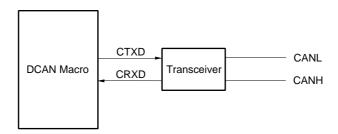

|      | 16.4  | Connec    | ction with Target System                     | 262 |

|      | 16.5  | CAN C     | ontroller Configuration                      | 262 |

|      | 16.6  | Special   | I Function Register for CAN-module           | 263 |

|      | 16.7  | Messag    | ge and Buffer Configuration                  | 264 |

|      | 16.8  | Transr    | nit Buffer Structure                         | 265 |

|      | 16.9  | Transm    | nit Message Format                           | 265 |

|      | 16.1  | 0 Receive | e Buffer Structure                           | 269 |

|      | 16.1  | 1 Receive | e Message Format                             | 270 |

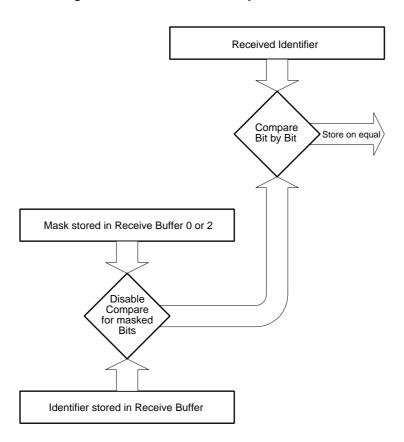

|      |       |           | unction                                      |     |

|      | 16.1  | 3 Operati | ion of the CAN Controller                    | 280 |

|      |       | 16.13.1   | CAN control register (CANC)                  | 280 |

|      |       | 16.13.2   | DCAN Error Status Register                   |     |

|      |       | 16.13.3   | CAN Transmit Error Counter                   |     |

|      |       | 16.13.4   | CAN Receive Error Counter                    |     |

|      |       | 16.13.5   | Message Count Register                       |     |

|      | 16.1  |           | te Generation                                |     |

|      |       |           | on Control                                   |     |

|      | . 5.1 | 16.15.1   | Transmit Control                             |     |

|      |       | 16.15.2   | Receive Control                              |     |

|      |       | 16.15.3   | Mask Control                                 |     |

|      |       | 16.15.4   | Special Functions                            |     |

|      | 16 1  |           | of Information                               |     |

|       | 16.16.1                | Interrupt Vectors                                                                                 | 304 |

|-------|------------------------|---------------------------------------------------------------------------------------------------|-----|

|       | 16.16.2                | Transmit Interrupt                                                                                | 304 |

|       | 16.16.3                | Receive Interrupt                                                                                 | 304 |

|       | 16.16.4                | Error Interrupt                                                                                   |     |

|       | 16.17 Influen          | ice of the standby Function of the CAN Controller                                                 |     |

|       | 16.17.1                | CPU Halt Mode                                                                                     |     |

|       | 16.17.2                | CPU Stop Mode                                                                                     |     |

|       | 16.17.3                | DCAN Sleep Mode                                                                                   |     |

|       | 16.17.4                | DCAN Stop Mode                                                                                    |     |

|       |                        | onal Description by Flowcharts                                                                    |     |

|       | 16.18.1                | Initialization                                                                                    |     |

|       | 16.18.2                | Transmit Preparation                                                                              |     |

|       | 16.18.3                | Abort Transmit                                                                                    |     |

|       | 16.18.4                | Handling by the DCAN                                                                              |     |

|       | 16.18.5                | Receive Event Oriented                                                                            |     |

|       | 16.18.6                | Receive Task Oriented                                                                             | 314 |

|       |                        |                                                                                                   |     |

| Chap  |                        | Controller / Driver                                                                               |     |

|       |                        | ontroller/Driver Functions                                                                        |     |

|       |                        | ontroller/Driver Configuration                                                                    |     |

|       |                        | ontroller/Driver Control Registers                                                                |     |

|       |                        | ontroller/Driver Settings                                                                         |     |

|       |                        | isplay Data Memory                                                                                |     |

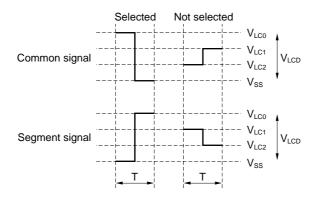

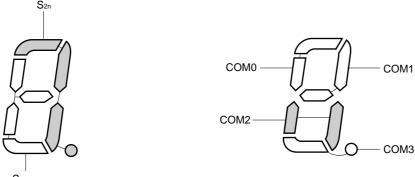

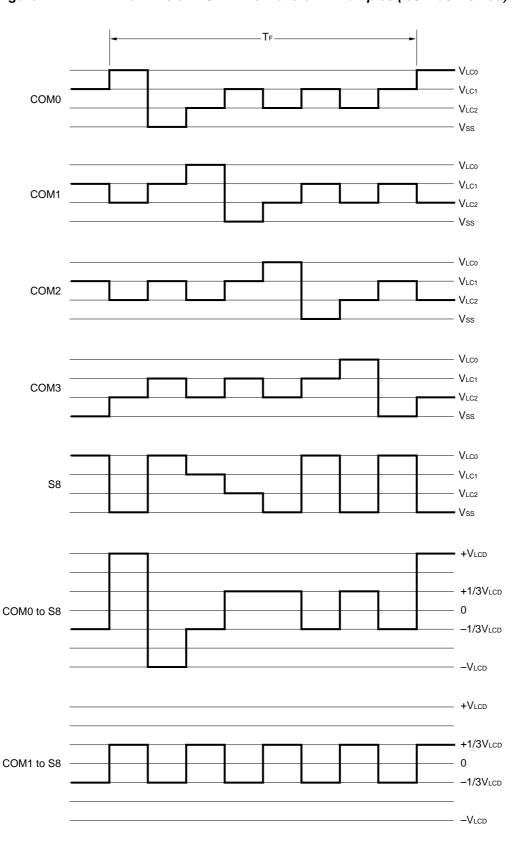

|       |                        | on Signals and Segment Signals                                                                    |     |

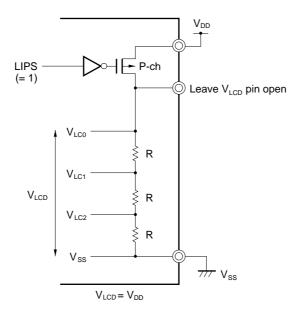

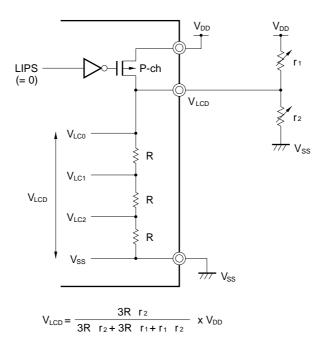

|       | 17.7 Supply            | ving LCD Drive Voltage V <sub>LC0</sub> , V <sub>LC1</sub> , and V <sub>LC2</sub>                 | 322 |

|       |                        | y Mode                                                                                            |     |

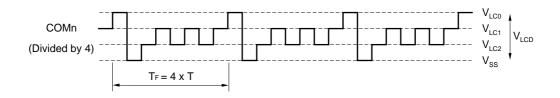

|       | 17.8.1                 | 4-time-division display example                                                                   |     |

|       |                        | ns on Emulation                                                                                   |     |

|       | 17.9.1                 | LCD timer control register (LCDTM)                                                                | 327 |

| Ch au | -t 10 Carr             | od Compretor                                                                                      | 220 |

| Cnap  |                        | nd Generator                                                                                      |     |

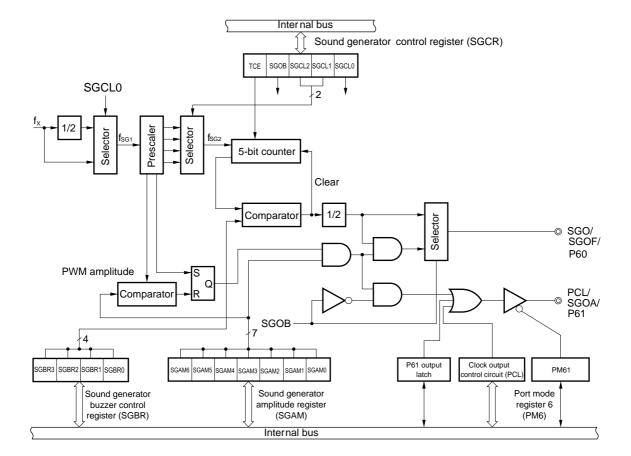

|       |                        | Generator Function                                                                                |     |

|       |                        | Generator Configuration                                                                           |     |

|       |                        | Generator Control Registers                                                                       |     |

|       |                        | Generator Operations                                                                              |     |

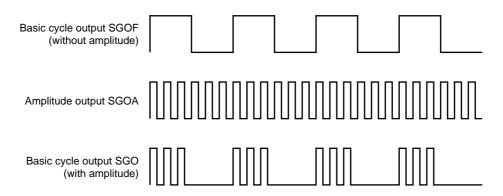

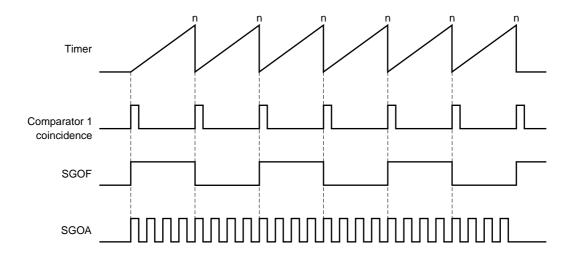

|       | 18.4.1                 | To output basic cycle signal SGOF (without amplitude)                                             |     |

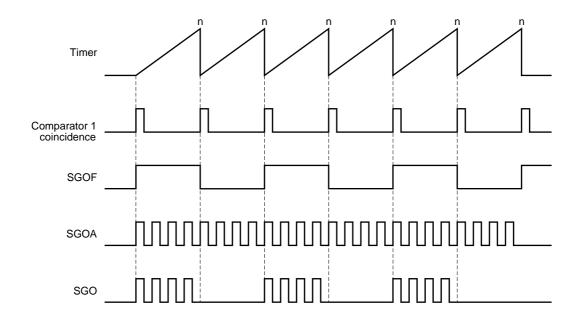

|       | 18.4.2                 | To output basic cycle signal SGO (with amplitude)                                                 | 336 |

| Ch au | -1 10 M-1-             | r Cantrallar / Driver                                                                             | 227 |

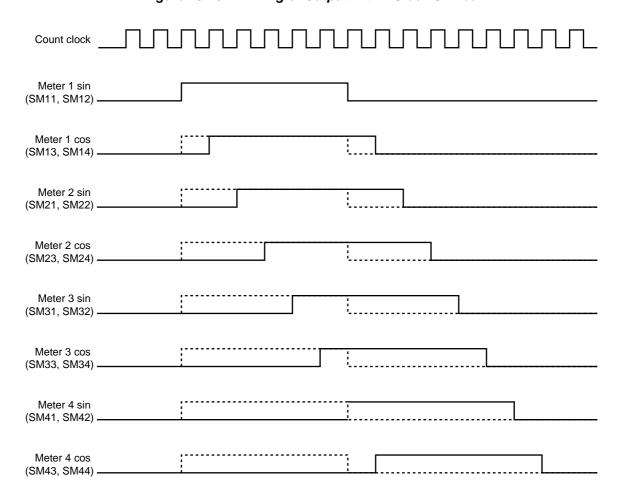

| Cnap  |                        | r Controller / Driver                                                                             |     |

|       |                        | Controller/Driver Functions                                                                       |     |

|       |                        | Controller/Driver Configuration                                                                   |     |

|       |                        | Controller/Driver Control Registers                                                               |     |

|       |                        | Controller/Driver Operations                                                                      |     |

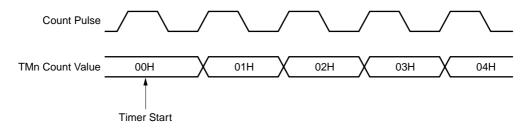

|       | 19.4.1                 | Basic operation of free-running up counter (SMCNT)                                                |     |

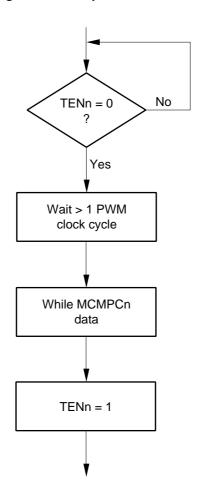

|       | 19.4.2                 | Update of PWM data                                                                                |     |

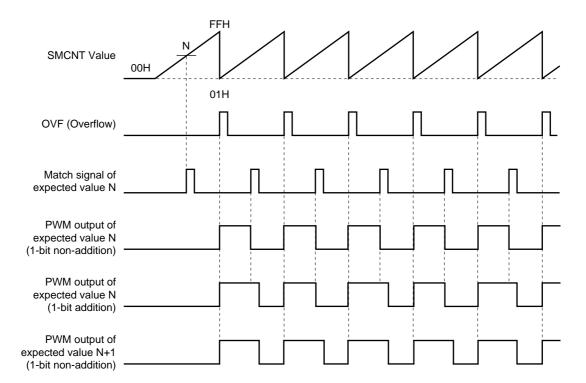

|       | 19.4.3                 | PWM output operation (output with 1 clock shifted)                                                |     |

|       | 19.4.4                 | PWW output operation (output with 1 clock shifted)                                                | 348 |

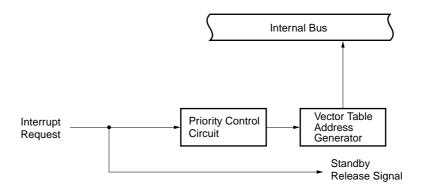

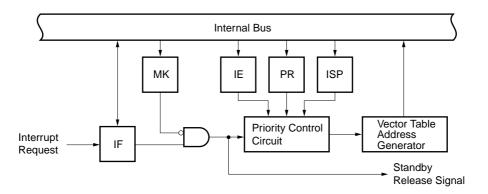

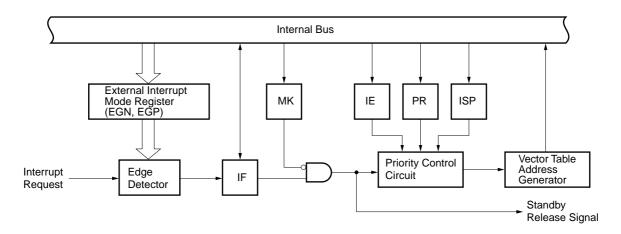

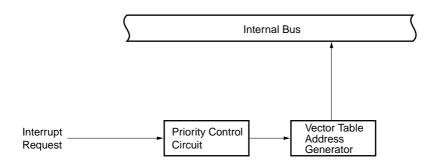

| Char  | ntor 20 Intor          | rupt Functions                                                                                    | 251 |

| Ullap |                        | •                                                                                                 |     |

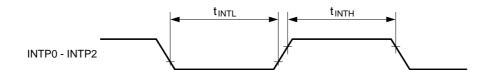

|       |                        | pt Function Types                                                                                 |     |

|       |                        | pt Sources and Configuration                                                                      |     |

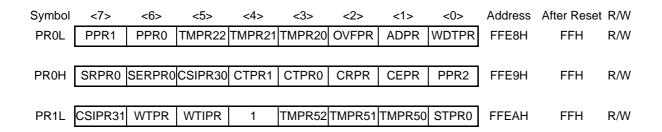

|       |                        | pt Function Control Registers                                                                     |     |

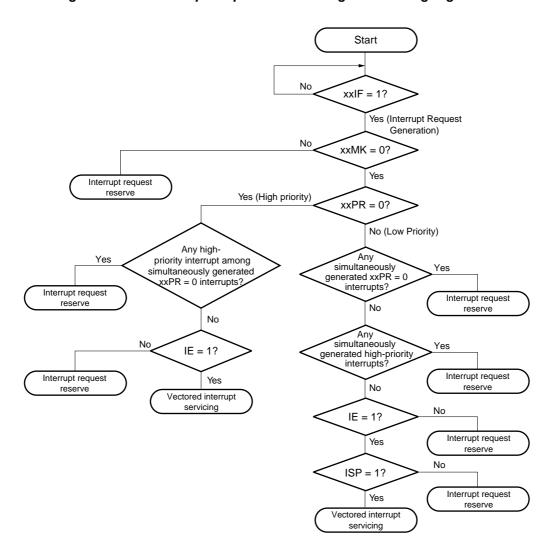

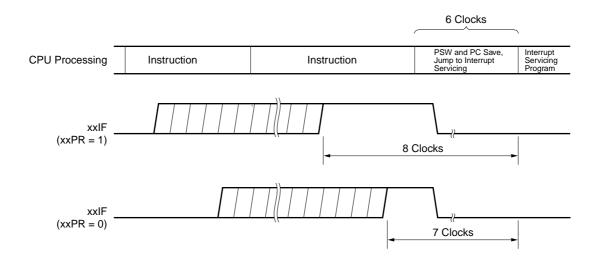

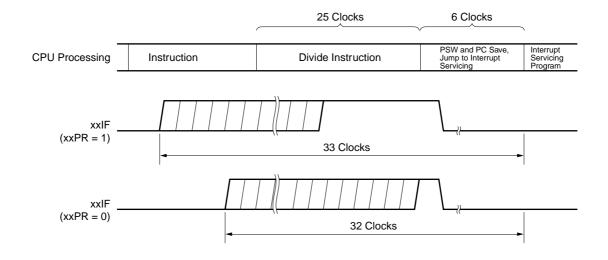

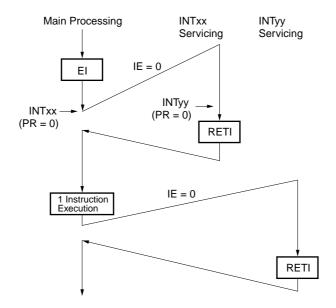

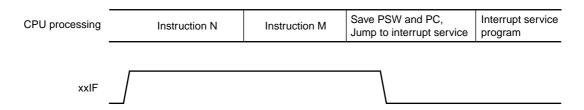

|       | 20.4 Interru<br>20.4.1 | pt Servicing Operations                                                                           |     |

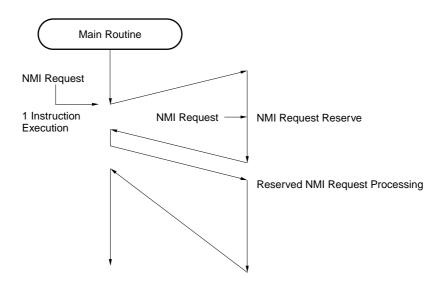

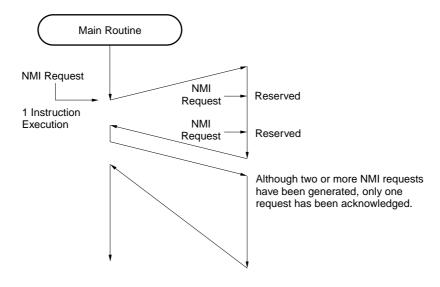

|       | 20.4.1                 | Non-maskable interrupt request acknowledge operation                                              |     |

|       | 20.4.2                 | Maskable interrupt request acknowledge operation Software interrupt request acknowledge operation |     |

|       | 20.4.3                 | , ,                                                                                               |     |

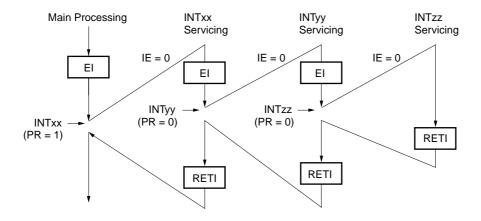

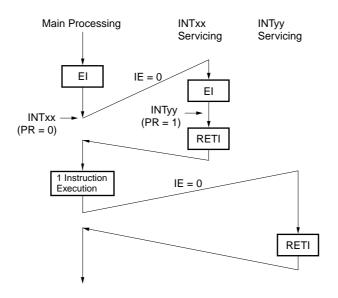

|       | 20.4.4<br>20.4.5       | Multiple interrupt servicing                                                                      | 370 |

|       | 70.40                  | UNELLUM TERMEST TESELVE                                                                           | 3/1 |

| Chapter 21 Star  | ndby Function                                                           | 373 |

|------------------|-------------------------------------------------------------------------|-----|

| 21.1 Stand       | by Function and Configuration                                           | 373 |

| 21.1.1           | Standby function                                                        |     |

| 21.1.2           | Standby function control register                                       |     |

| 21.2 Stand       | by Function Operations                                                  |     |

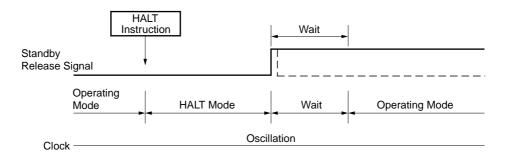

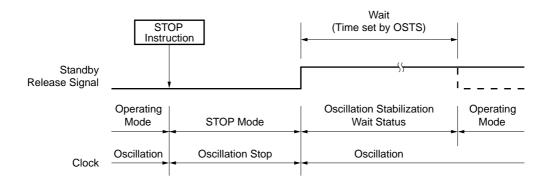

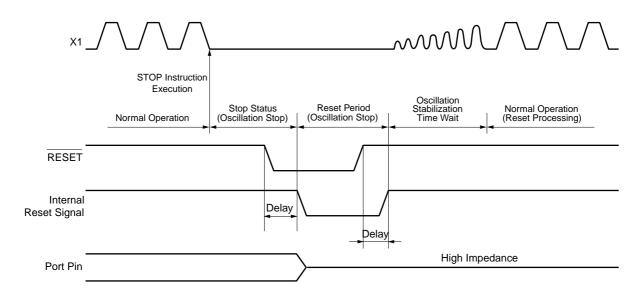

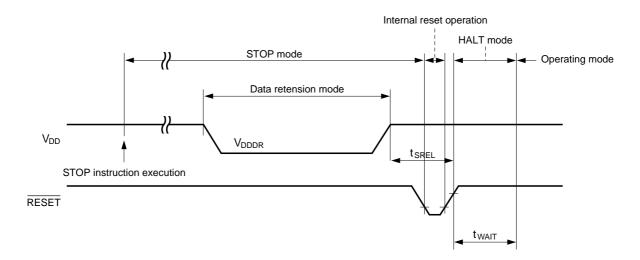

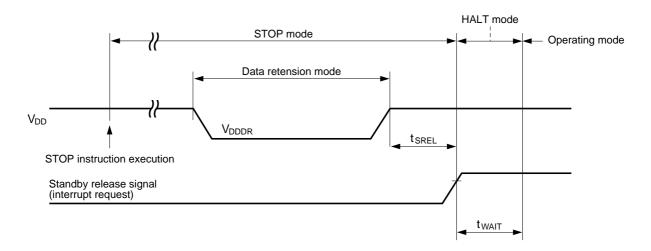

| 21.2.1           | HALT mode                                                               |     |

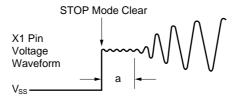

| 21.2.2           | STOP mode                                                               |     |

|                  |                                                                         |     |

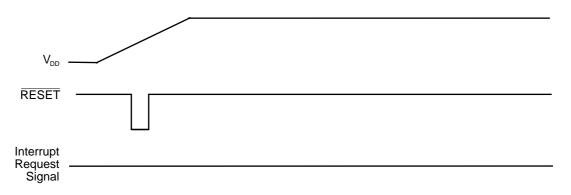

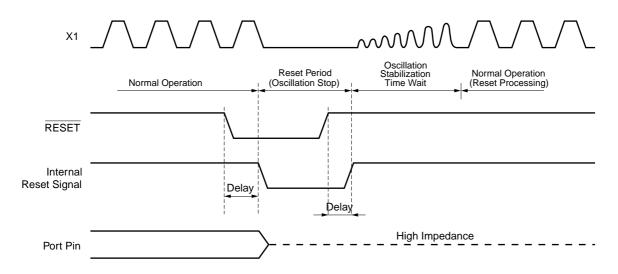

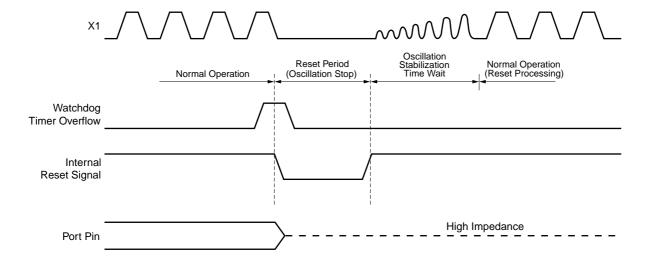

| Chapter 22 Res   | et Function                                                             | 381 |

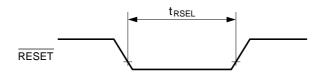

| 22.1 Reset       | Function                                                                | 381 |

|                  |                                                                         |     |

| Chapter 23 µPD   | 78F0828A and Memory Definition                                          | 387 |

| 23.1 Memo        | ory Size Switching Register (IMS)                                       | 388 |

| 23.2 Intern      | al Expansion RAM Size Switching Register                                | 389 |

| 23.3 Self-P      | Programming and Oscillation Control Register                            | 390 |

| 23.4 Flash       | memory programming with flash programmer                                |     |

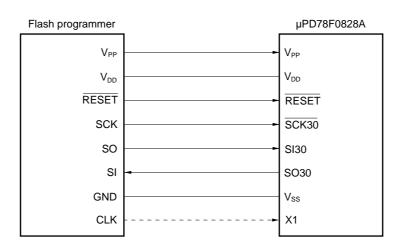

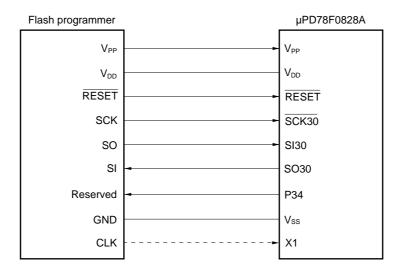

| 23.4.1           | Selection of transmission method                                        |     |

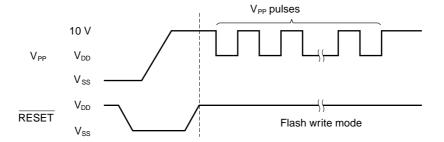

| 23.4.2           | Initialization of the programming mode                                  | 391 |

| 23.4.3           | Flash memory programming function                                       | 392 |

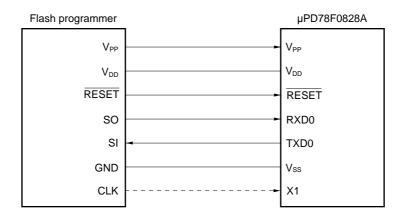

| 23.4.4           | Flash programmer connection                                             | 393 |

| 23.4.5           | Flash programming precautions                                           | 394 |

| 23.5 Flash       | Self-Programming Control                                                | 395 |

| 23.5.1           | Flash Self-Programming Mode Control Register                            | 395 |

|                  |                                                                         |     |

| Chapter 24 Insti | ruction Set                                                             | 397 |

| 24.1 Legen       | nds Used in Operation List                                              | 397 |

| 24.1.1           | Operand identifiers and description methods                             | 397 |

| 24.1.2           | Description of "operation" column                                       | 398 |

| 24.2 Opera       | tion List                                                               | 399 |

| 24.3 Instru      | ctions Listed by Addressing Type                                        | 407 |

|                  |                                                                         |     |

|                  | trical Specifications                                                   |     |

|                  | ute Maximum Ratings                                                     |     |

|                  | citance                                                                 |     |

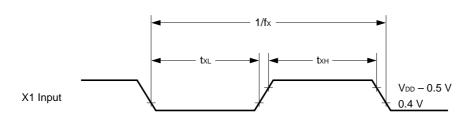

|                  | System Clock Oscillation Circuit Characteristics                        |     |

|                  | naracteristics                                                          |     |

|                  | naracteristics                                                          | 432 |

| 25.5.1           | Basic Operation                                                         |     |

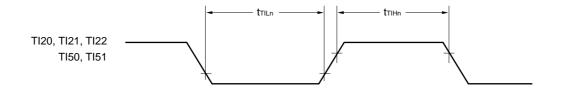

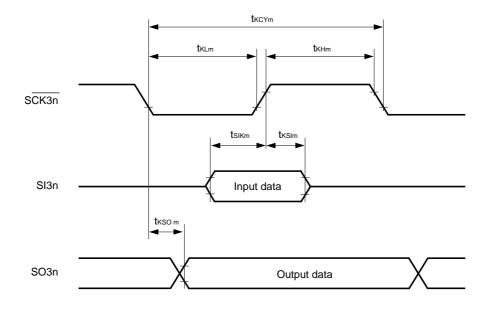

| 25.5.2           | Serial Interface                                                        |     |

| 25.5.3           | Sound Generator Characteristics                                         |     |

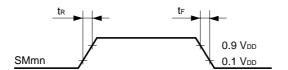

| 25.5.4           | Meter Controller / Driver Characteristics                               |     |

| 25.5.5           | A/D Converter Characteristics                                           |     |

| 25.5.6           | Data Memory Stop Mode Low Supply Voltage Data Retention Characteristics |     |

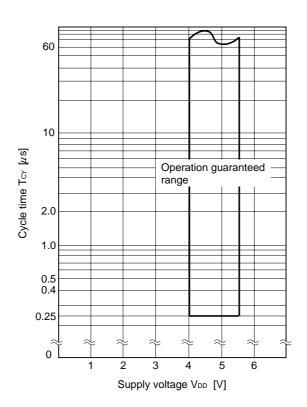

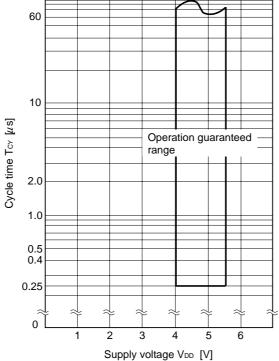

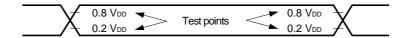

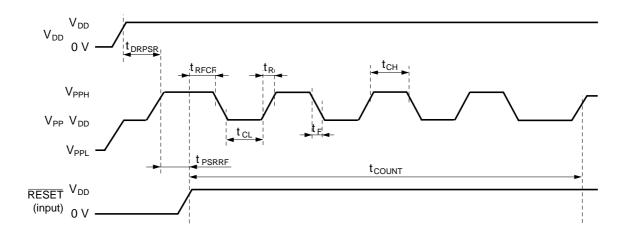

| 25.5.7           | Flash Memory Programming Characteristics: µPD78F0828A(A)                | 450 |

|                  |                                                                         |     |

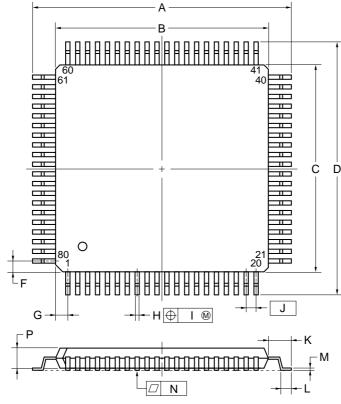

| Chapter 26 Pacl  | kage Drawing                                                            | 453 |

|                  |                                                                         |     |

| Chapter 27 Rec   | ommended Soldering Conditions                                           | 455 |

|                  |                                                                         |     |

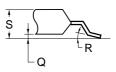

| Appendix A Deve  | elopment Tools                                                          | 457 |

|                  | -                                                                       |     |

| Appendix R Fmh   | pedded Software                                                         | 463 |

| -                |                                                                         |     |

| Annondiy C Inda  | ex                                                                      | 105 |

| Appendix C inde  | ;A                                                                      | 403 |

|                  |                                                                         |     |

| Appendix D Revi  | ision History                                                           | 469 |

# **List of Figures**

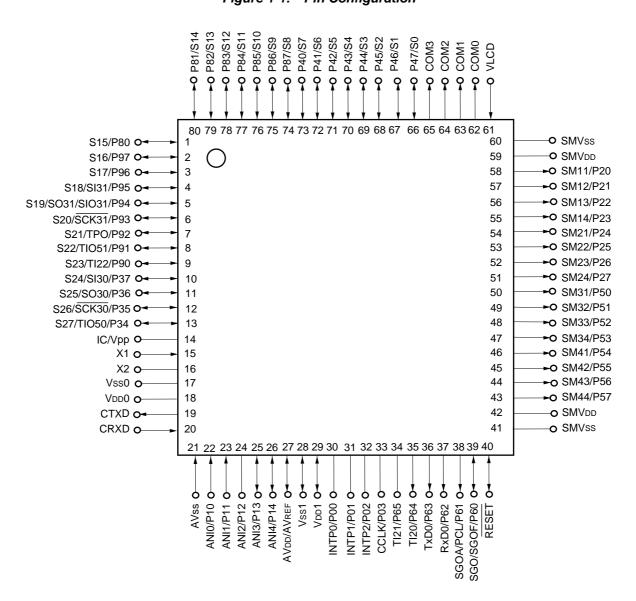

| Figure 1-1:  | Pin Configuration                                     | 27  |

|--------------|-------------------------------------------------------|-----|

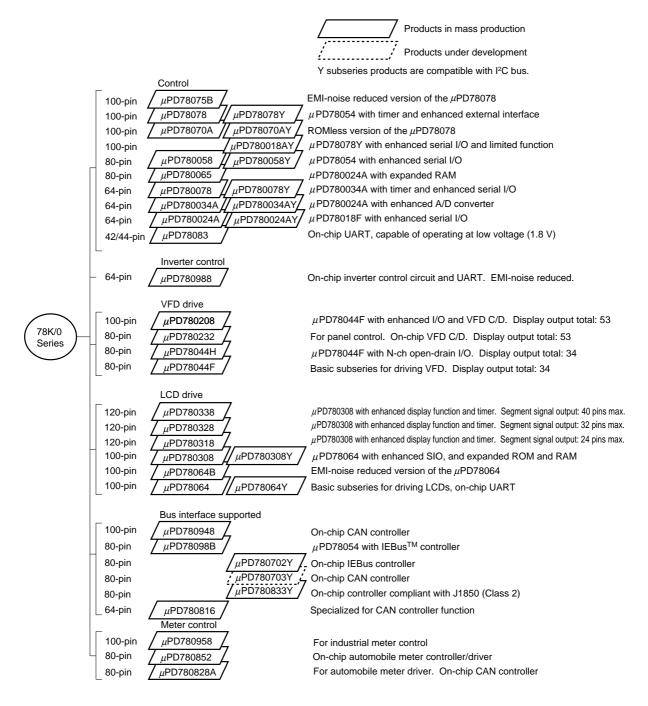

| Figure 1-2:  | 78K/0 Series Expansion                                | 29  |

| Figure 1-3:  | Block Diagram                                         | 31  |

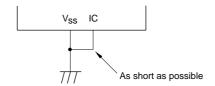

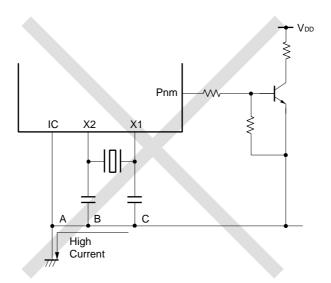

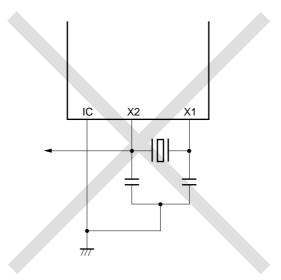

| Figure 2-1:  | Connection of IC Pins                                 | 44  |

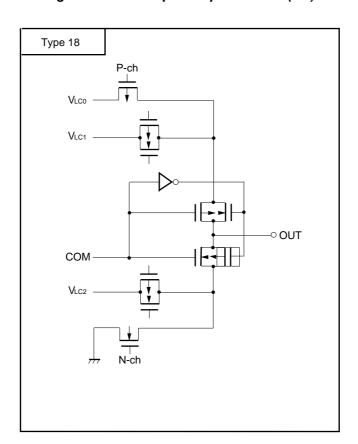

| Figure 2-2:  | Pin Input/Output Circuits (1/3)                       | 47  |

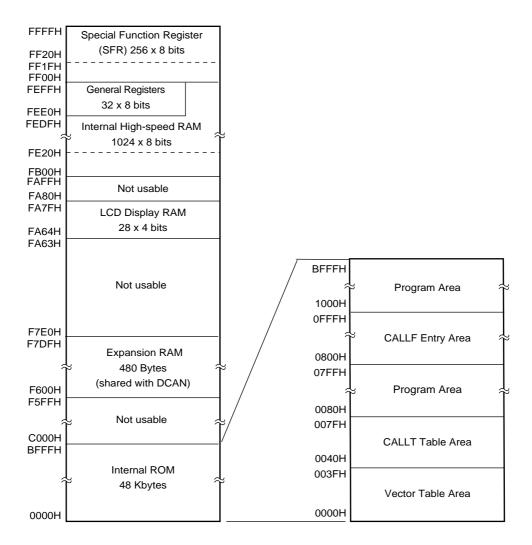

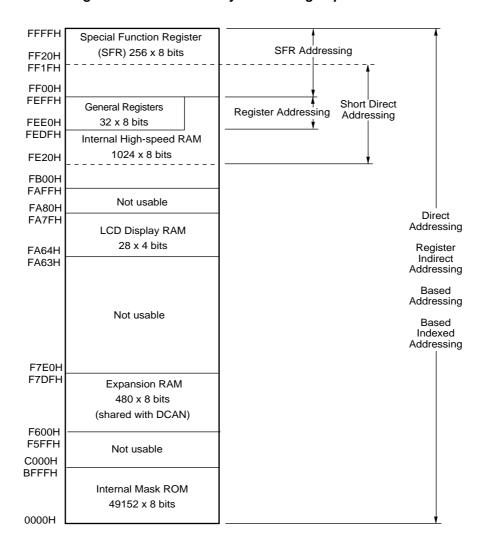

| Figure 3-1:  | Memory Map of the μPD780824A                          | 51  |

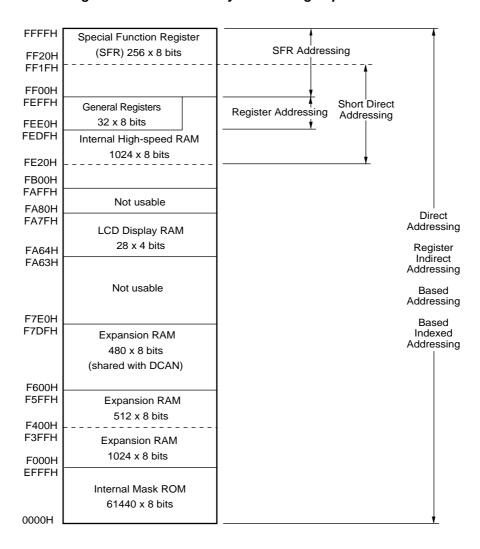

| Figure 3-2:  | Memory Map of the μPD780826A                          | 52  |

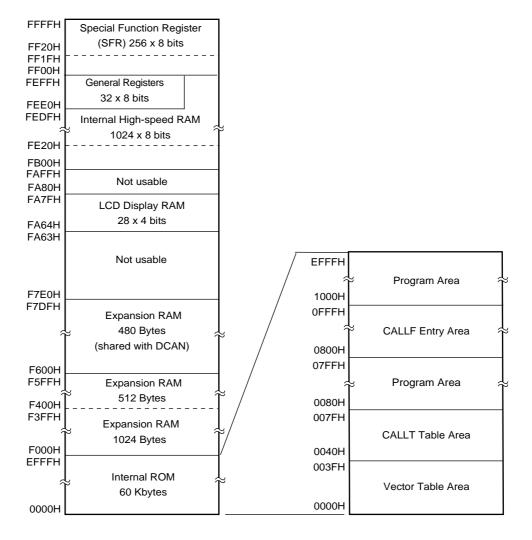

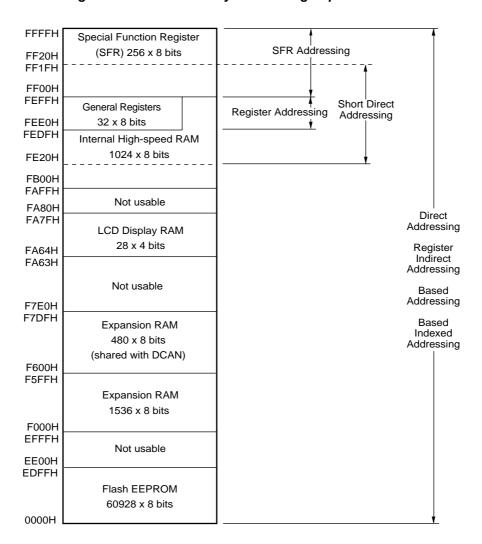

| Figure 3-3:  | Memory Map of the μPD780828A                          | 53  |

| Figure 3-4:  | Memory Map of the µPD78F0828A                         |     |

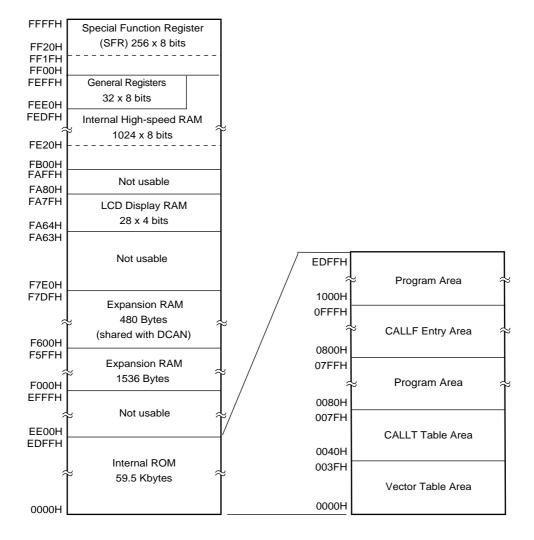

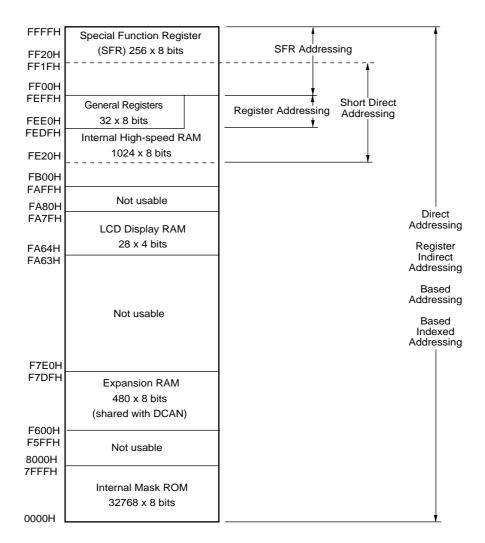

| Figure 3-5:  | Data Memory Addressing of µPD780824A                  | 58  |

| Figure 3-6:  | Data Memory Addressing of µPD780826A                  |     |

| Figure 3-7:  | Data Memory Addressing of µPD780828A                  | 60  |

| Figure 3-8:  | Data Memory Addressing of µPD78F0828A                 | 61  |

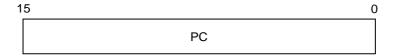

| Figure 3-9:  | Program Counter Configuration                         | 62  |

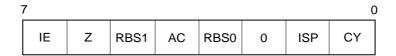

| Figure 3-10: | Program Status Word Configuration                     |     |

| Figure 3-11: | Stack Pointer Configuration                           |     |

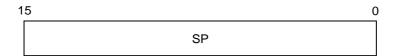

| Figure 3-12: | Data to be Saved to Stack Memory                      |     |

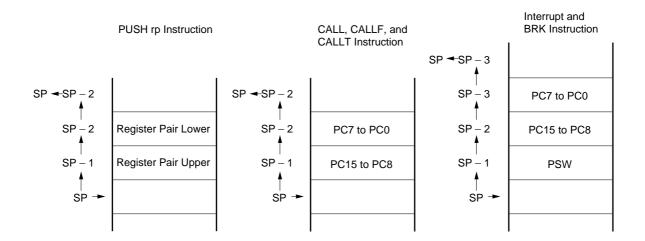

| Figure 3-13: | Data to be Reset to Stack Memory                      |     |

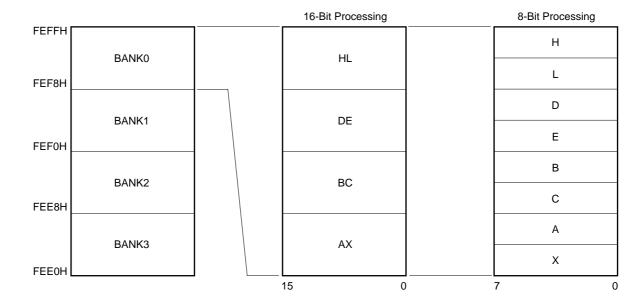

| Figure 3-14: | General Register Configuration                        | 65  |

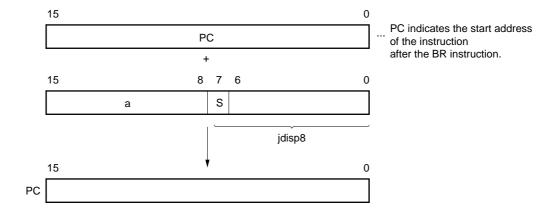

| Figure 3-15: | Relative Addressing                                   |     |

| Figure 3-16: | Immediate Addressing                                  |     |

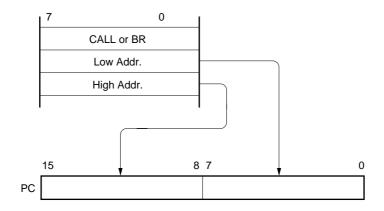

| Figure 3-17: | Table Indirect Addressing                             |     |

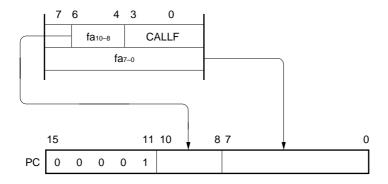

| Figure 3-18: | Register Addressing                                   |     |

| Figure 3-19: | Register Addressing                                   |     |

| Figure 3-20: | Direct addressing                                     |     |

| Figure 3-21: | Short direct addressing                               |     |

| Figure 3-22: | Special-Function Register (SFR) Addressing            |     |

| Figure 3-23: | Register indirect addressing                          |     |

| Figure 3-24: | Based addressing description example                  |     |

| Figure 3-25: | Based indexed addressing description example          |     |

| Figure 3-26: | Stack addressing description example                  |     |

| Figure 4-1:  | Port Types                                            |     |

| Figure 4-2:  | P00 to P03 Configurations                             |     |

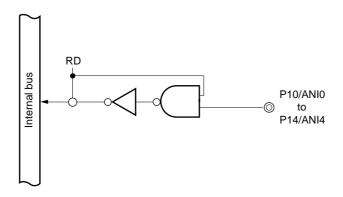

| Figure 4-3:  | P10 to P14 Configurations                             |     |

| Figure 4-4:  | P20 to P27 Configurations                             |     |

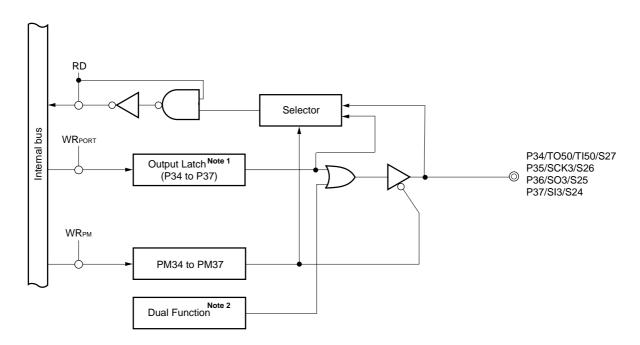

| Figure 4-5:  | P34 to P37 Configurations                             |     |

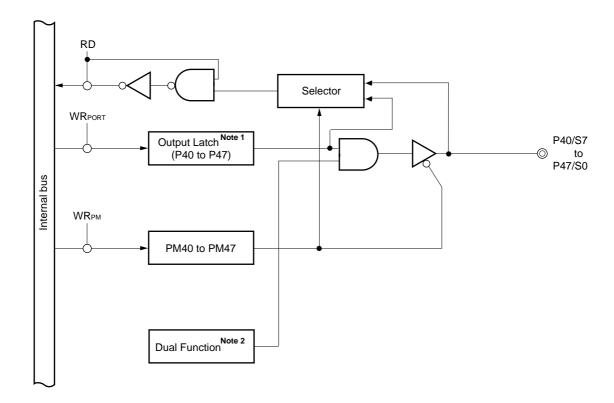

| Figure 4-6:  | P40 to P47 Configurations                             |     |

| Figure 4-7:  | P50 to P57 Configurations                             |     |

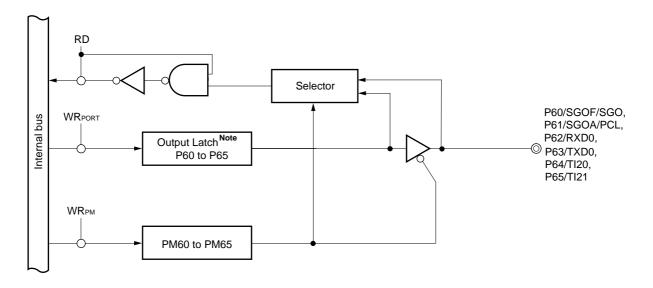

| Figure 4-8:  | P60 to P65 Configurations                             |     |

| Figure 4-9:  | P80 to P87 Configurations                             |     |

| Figure 4-10: | P90 to P97 Configurations                             |     |

| Figure 4-11: | Port Mode Register Format                             |     |

| Figure 4-12: | Pull-Up Resistor Option Register (PUm) Format         |     |

| Figure 4-13: | Port Function Register (PF3, PF4, PF8 and PF9) Format |     |

| Figure 5-1:  | Block Diagram of Clock Generator                      |     |

| Figure 5-2:  | Processor Clock Control Register Format               |     |

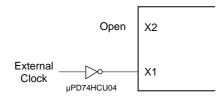

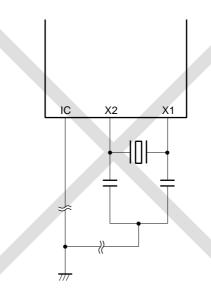

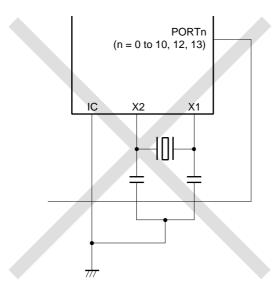

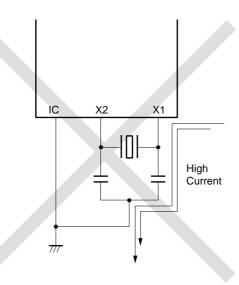

| Figure 5-3:  | External Circuit of Main System Clock Oscillator      |     |

| Figure 5-4:  | Examples of Oscillator with Bad Connection (1/3)      |     |

| Figure 5-5:  | System Clock and CPU Clock Switching                  |     |

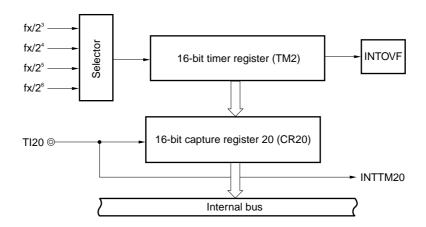

| Figure 6-1:  | Timer 2 (TM2) Block Diagram                           |     |

| Figure 6-2:  | 16-Bit Timer Mode Control Register (TMC2) Format      |     |

| Figure 6-3:  | Capture Pulse Control Register (CRC2) Format          |     |

| Figure 6-4:  | Prescaler Mode Register (PRM2) Format                 |     |

| Figure 6-5:  | Configuration Diagram for Pulse Width Measurement     |     |

| 9 0 0.       | by Using the Free Running Counter                     | 119 |

|              | , , , ,                                               |     |

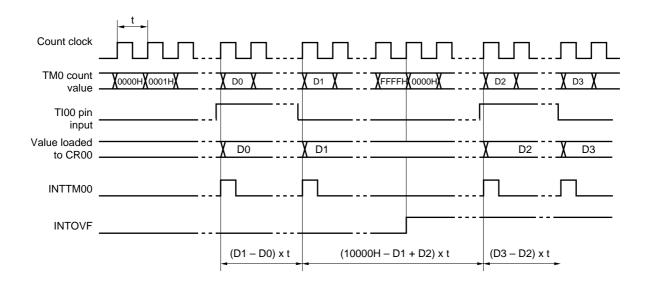

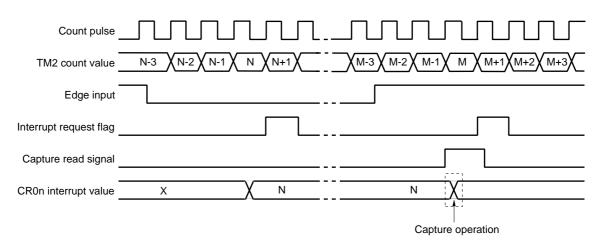

| Figure 6-6:                  | Timing of Pulse Width Measurement Operation by Using the Free Running Counter and One Capture Register (with Both Edges Specified) | . 120 |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|

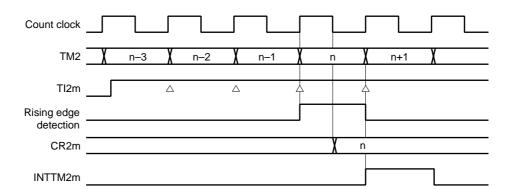

| Figure 6-7:                  | CR2m Capture Operation with Rising Edge Specified                                                                                  |       |

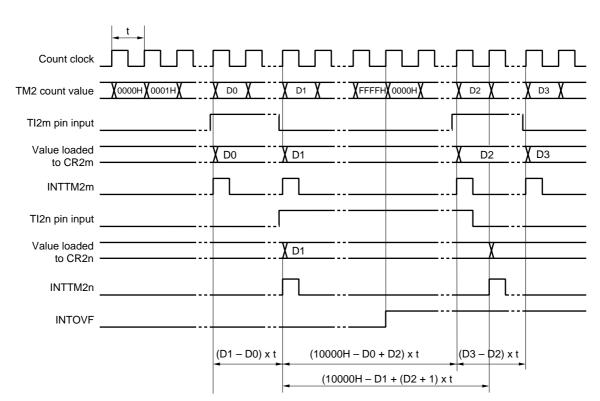

| Figure 6-8:                  | Timing of Pulse Width Measurement Operation by Free Running Counter                                                                |       |

| Ü                            | (with Both Edges Specified)                                                                                                        | . 122 |

| Figure 6-9:                  | 16-Bit Timer Register Start Timing                                                                                                 |       |

| Figure 6-10:                 | Capture Register Data Retention Timing                                                                                             |       |

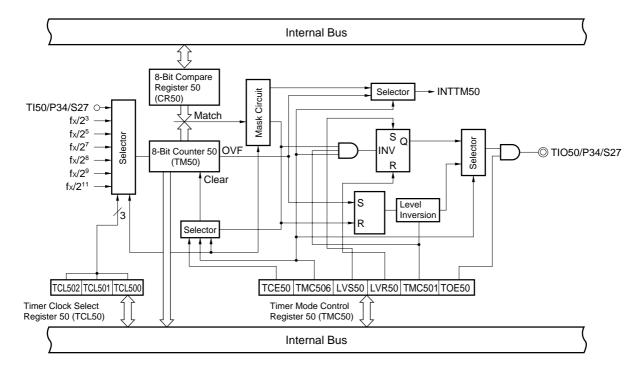

| Figure 7-1:                  | 8-Bit Timer/Event Counter 50 Block Diagram                                                                                         |       |

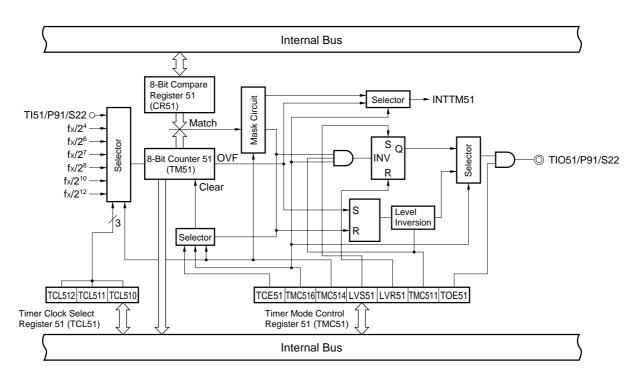

| Figure 7-2:                  | 8-Bit Timer/Event Counter 51 Block Diagram                                                                                         |       |

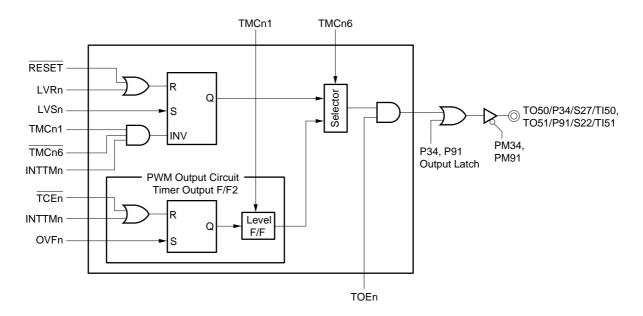

| Figure 7-3:                  | Block Diagram of 8-Bit Timer/Event Counters 50 and 51 Output Control Circuit                                                       |       |

| Figure 7-4:                  | Timer Clock Select Register 50 Format                                                                                              |       |

| Figure 7-5:                  | Timer Clock Select Register 51 Format                                                                                              |       |

| Figure 7-6:                  | 8-Bit Timer Mode Control Register 50 Format                                                                                        |       |

| Figure 7-7:                  | 8-Bit Timer Mode Control Register 51 Format (1/2)                                                                                  |       |

| Figure 7-8:                  | Port Mode Register 3 Format                                                                                                        |       |

| Figure 7-9:                  | Port Mode Register 9 Format                                                                                                        |       |

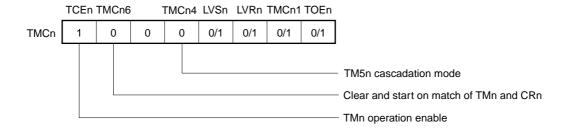

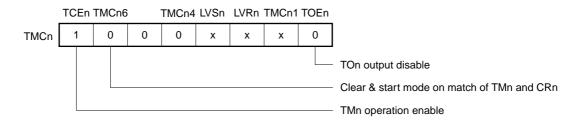

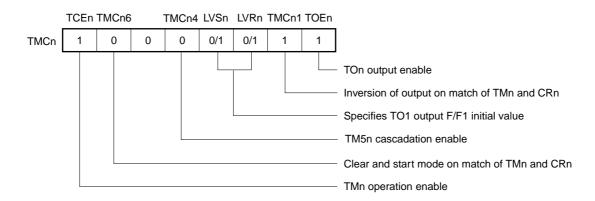

| Figure 7-10:                 | 8-Bit Timer Mode Control Register Settings for Interval Timer Operation                                                            |       |

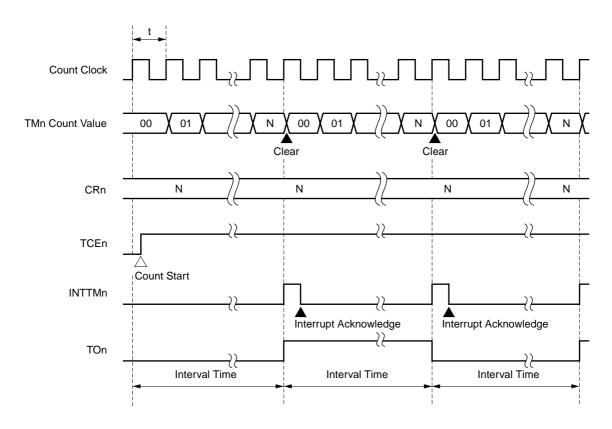

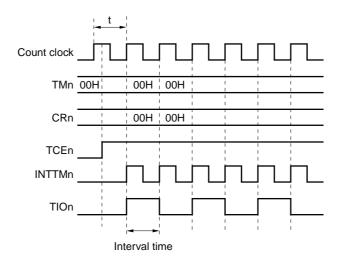

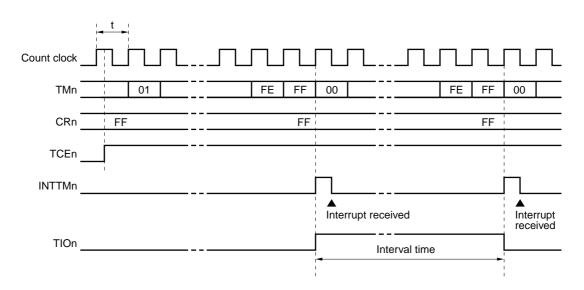

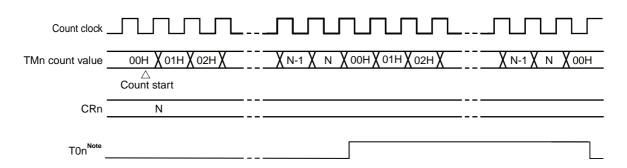

| Figure 7-11:                 | Interval Timer Operation Timings (1/3)                                                                                             |       |

| Figure 7-12:                 | 8-Bit Timer Mode Control Register Setting for External Event Counter Operation                                                     |       |

| Figure 7-13:                 | External Event Counter Operation Timings (with Rising Edge Specified)                                                              |       |

| Figure 7-14:                 | 8-Bit Timer Mode Control Register Settings for Square-Wave Output Operation                                                        |       |

| Figure 7-15:                 | Square-wave Output Operation Timing                                                                                                |       |

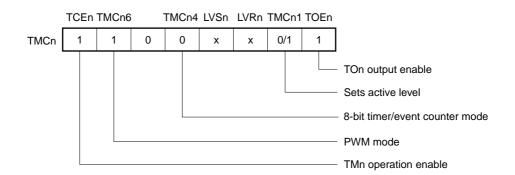

| Figure 7-16:                 | 8-Bit Timer Control Register Settings for PWM Output Operation                                                                     |       |

| Figure 7-17:                 | PWM Output Operation Timing (Active high setting)                                                                                  |       |

| Figure 7-18:                 | PWM Output Operation Timings (CRn0 = 00H, active high setting)                                                                     |       |

| Figure 7-19:                 | PWM Output Operation Timings (CRn = FFH, active high setting)                                                                      |       |

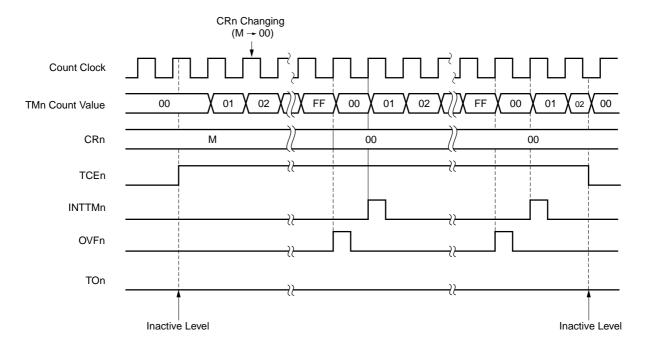

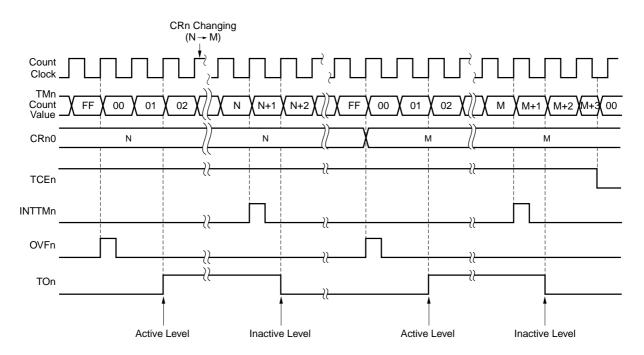

| Figure 7-20:                 | PWM Output Operation Timings (CRn changing, active high setting)                                                                   |       |

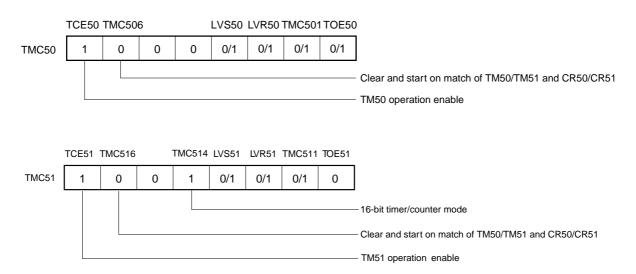

| Figure 7-21:                 | 8-Bit Timer Mode Control Register Settings for 16-Bit Interval Timer Operation                                                     |       |

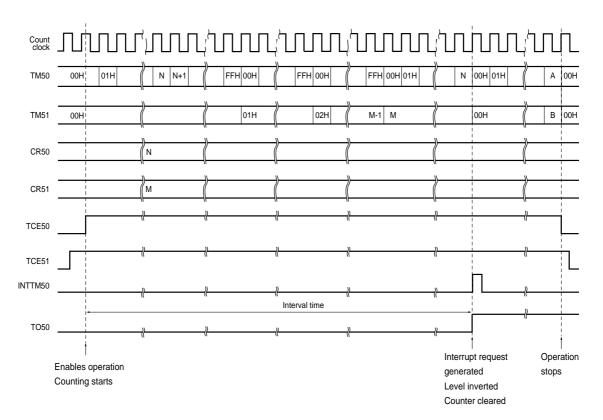

| Figure 7-21:                 | 16-Bit Resolution Cascade Mode (with TM50 and TM51)                                                                                |       |

| Figure 7-23:                 | 8-bit Timer Registers 50 and 51 Start Timings                                                                                      |       |

| Figure 7-24:                 | External Event Counter Operation Timings                                                                                           |       |

| Figure 7-25:                 | Timings after Compare Register Change during Timer Count Operation                                                                 |       |

| Figure 8-1:                  | 8-Bit Timer/Event Counter 52 Block Diagram                                                                                         |       |

| Figure 8-2:                  | Timer Clock Select Register 52 Format                                                                                              |       |

| Figure 8-3:                  | 8-Bit Timer Output Control Register Format                                                                                         |       |

| Figure 8-4:                  | 8-Bit Timer Mode Control Register Settings for Interval Timer Operation                                                            |       |

| Figure 8-5:                  | Interval Timer Operation Timings (1/3)                                                                                             |       |

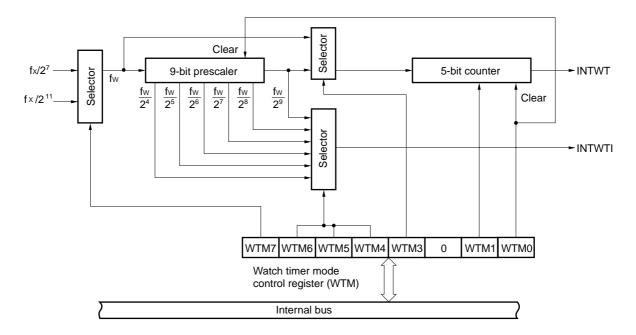

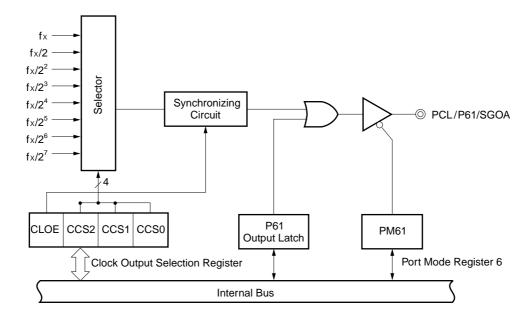

| Figure 9-1:                  | Block Diagram of Watch Timer                                                                                                       | 163   |

| Figure 9-1:                  | Watch Timer Mode Control Register (WTM) Format (1/2)                                                                               |       |

| Figure 9-2:                  | Operation Timing of Watch Timer/Interval Timer                                                                                     |       |

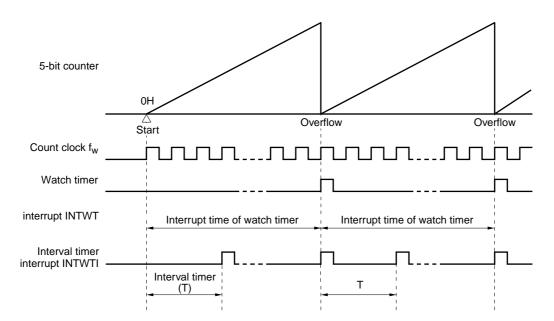

| Figure 10-1:                 | Watchdog Timer Block Diagram                                                                                                       |       |

| Figure 10-1:                 | Timer Clock Select Register 2 Format                                                                                               |       |

| Figure 10-3:                 | Watchdog Timer Mode Register Format                                                                                                |       |

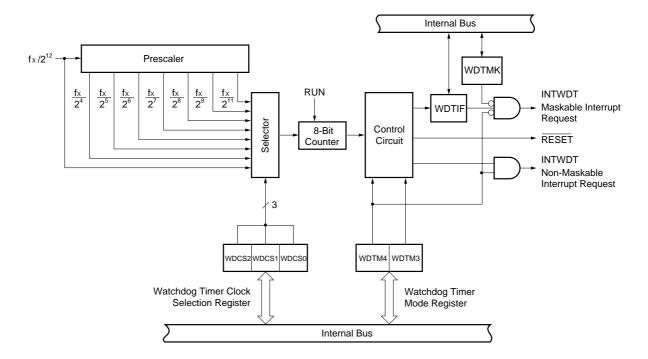

| Figure 11-1:                 | Remote Controlled Output Application Example                                                                                       |       |

| Figure 11-2:                 | Clock Output Control Circuit Block Diagram                                                                                         |       |

| Figure 11-3:                 | Timer Clock Select Register 0 Format                                                                                               |       |

| Figure 11-4:                 | Port Mode Register 6 Format                                                                                                        |       |

| Figure 11-4.                 | A/D Converter Block Diagram                                                                                                        |       |

| Figure 12-1:                 | Power-Fail Detection Function Block Diagram                                                                                        |       |

| Figure 12-3:                 | A/D Converter Mode Register (ADM1) Format                                                                                          |       |

| -                            | Analog Input Channel Specification Register (ADS1) Format                                                                          |       |

| Figure 12-4:                 | Power-Fail Compare Mode Register (PFM) Format                                                                                      |       |

| Figure 12-5:                 | Power-fail compare threshold value register (PFT)                                                                                  |       |

| Figure 12-6:                 | Basic Operation of 8-Bit A/D Converter                                                                                             |       |

| Figure 12-7:<br>Figure 12-8: | Relation between Analog Input Voltage and A/D Conversion Result                                                                    |       |

| Figure 12-6.                 | A/D Conversion                                                                                                                     |       |

| Figure 12-9.                 | Example Method of Reducing Current Consumption in Standby Mode                                                                     |       |

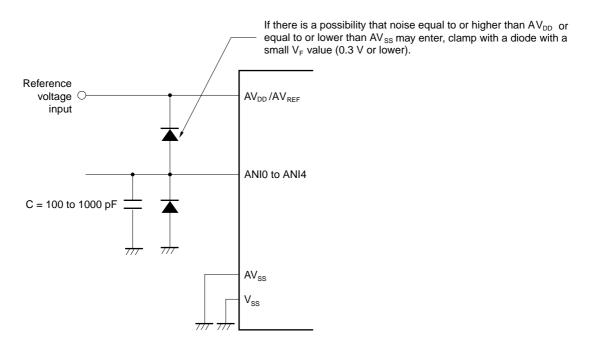

| Figure 12-10.                | Analog Input Pin Handling                                                                                                          | 192   |

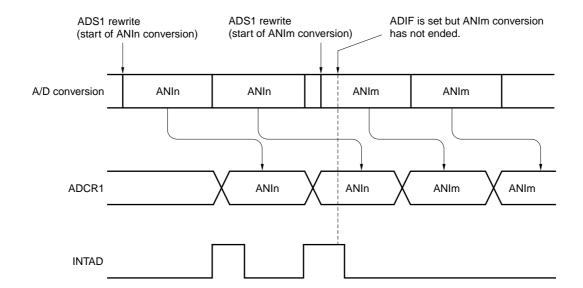

| Figure 12-12: | A/D Conversion End Interrupt Request Generation Timing                |     |

|---------------|-----------------------------------------------------------------------|-----|

| Figure 12-13: | D/A Converter Mode Register (DAM0) Format                             |     |

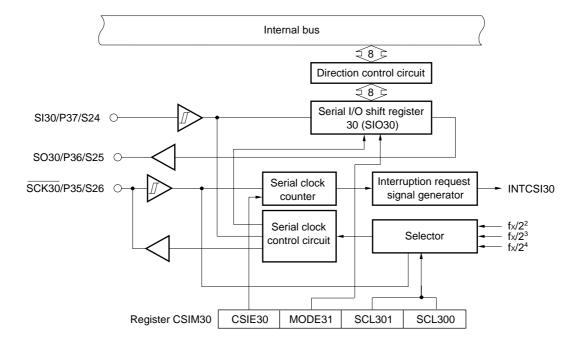

| Figure 13-1:  | Block Diagram of SIO30                                                |     |

| Figure 13-2:  | Format of Serial Operation Mode Register (CSIM30)                     |     |

| Figure 13-3:  | Format of Serial Operation Mode Register (CSIM30)                     |     |

| Figure 13-4:  | Format of Serial Operation Mode Register (CSIM30)                     | 201 |

| Figure 13-5:  | Timing of Three-wire Serial I/O Mode                                  | 202 |

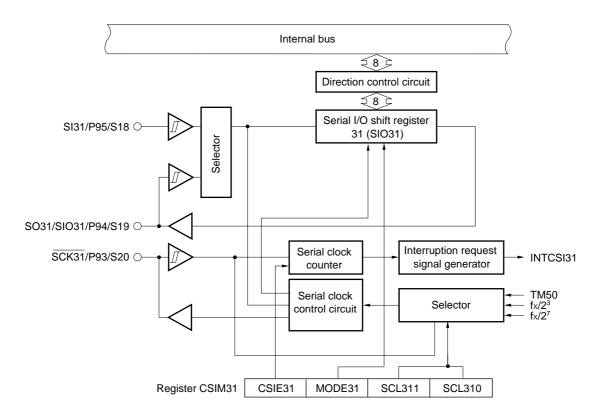

| Figure 14-1:  | Block Diagram of SIO31                                                |     |

| Figure 14-2:  | Format of Serial Operation Mode Register (CSIM31)                     | 208 |

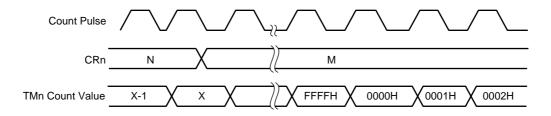

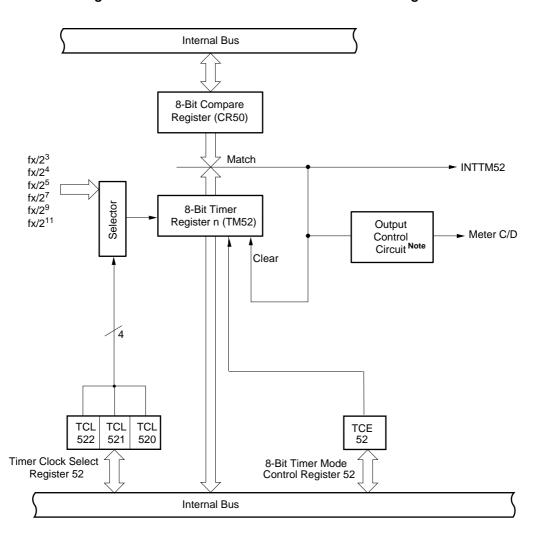

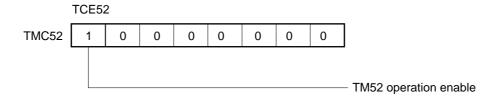

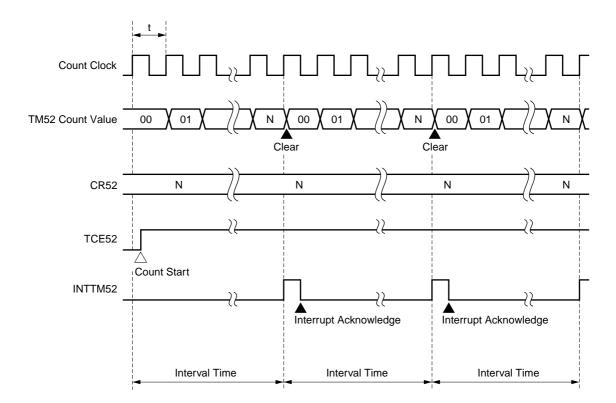

| Figure 14-3:  | Format of Serial Mode Switch Register (SIOSWI)                        | 209 |